5.3. Instruction set simulation

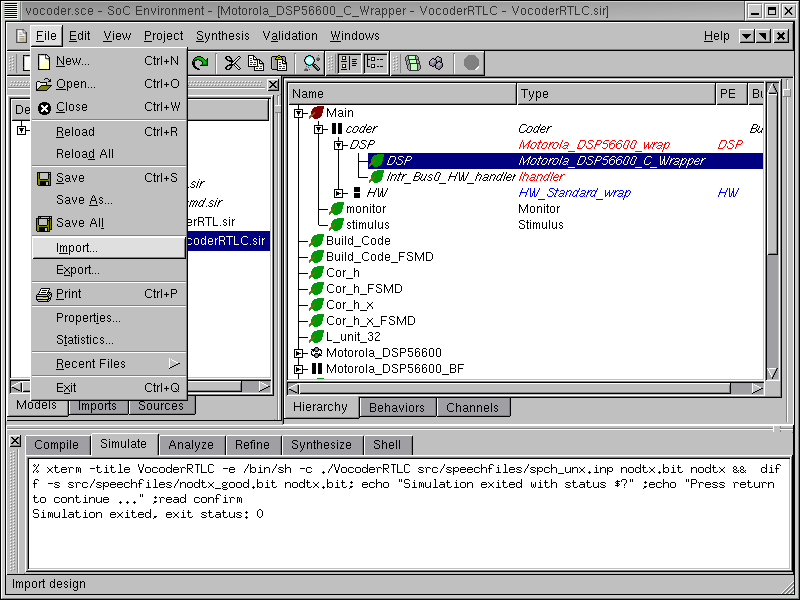

After we generated C code for the DSP, we compile the C code into DSP's instruction set and import the instruction set simulator (ISS) for the Motorola DSP56600. To start importing, select File->Import from the menu bar.

5.3.1. Import instruction set simulator model

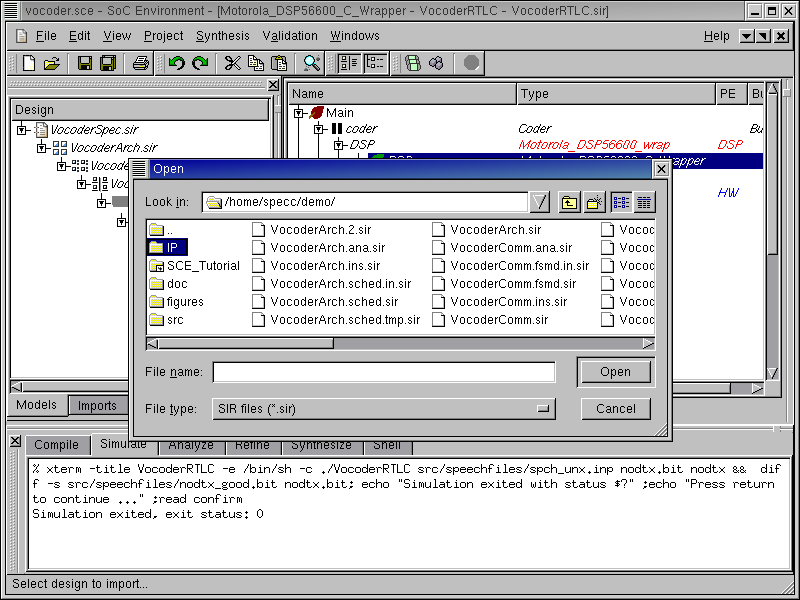

Select directory "IP" from the file selection menu by double Left click.

5.3.1.1. Import instruction set simulator model (cont'd)

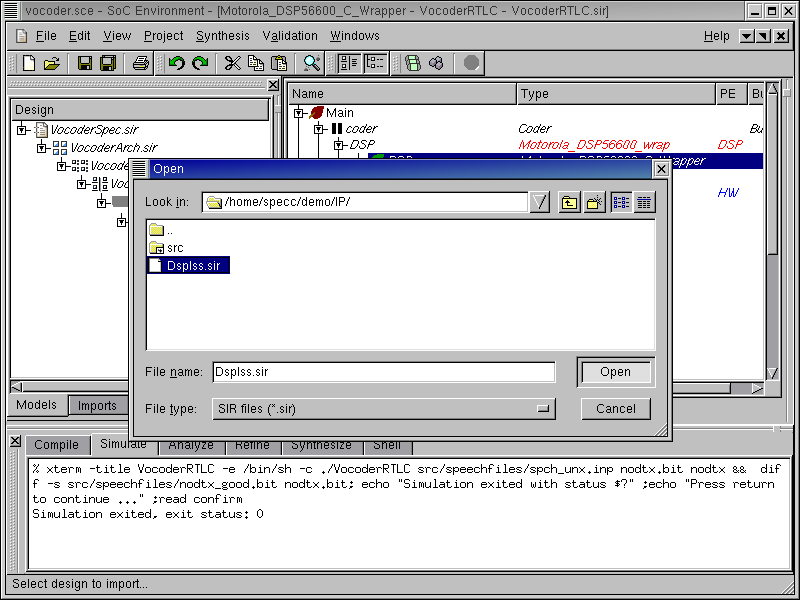

Inside directory IP, select "DspIss.sir" and Left click on Open.

The SIR file contains the instruction set simulator for our chosen DSP. The behavior loads the compiled object code for the tasks that were mapped to DSP and executes it on the instruction set simulator.

5.3.1.2. Import instruction set simulator model (cont'd)

Once "DspIss.sir" is imported, we can notice behavior "DspISS" as a new root behavior in the design hierarchy tree. This is because behavior "DspISS" has not been instantiated yet.

5.3.1.3. Import instruction set simulator model (cont'd)

In the design hierarchy tree, select behavior "DSP". Right click and select Change Type.

5.3.1.4. Import instruction set simulator model (cont'd)

The type of behavior "DSP" may now be changed by selecting DspISS.

By doing this, we have now refined the software part of our design to be implemented with the DSP56600 processor's instruction set. Recall that the software part mapped to DSP has already been compiled for the DSP56600 processor and the object file is ready. As mentioned earlier, the new behavior will load this object file and execute it on the DSP's instruction set simulator. Thus the model becomes clock cycle accurate.

5.3.2. Simulate cycle accurate model

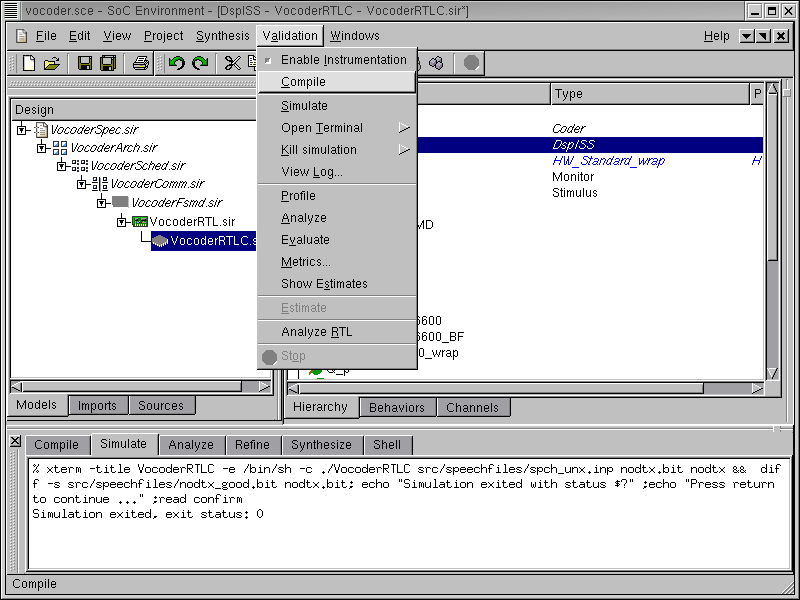

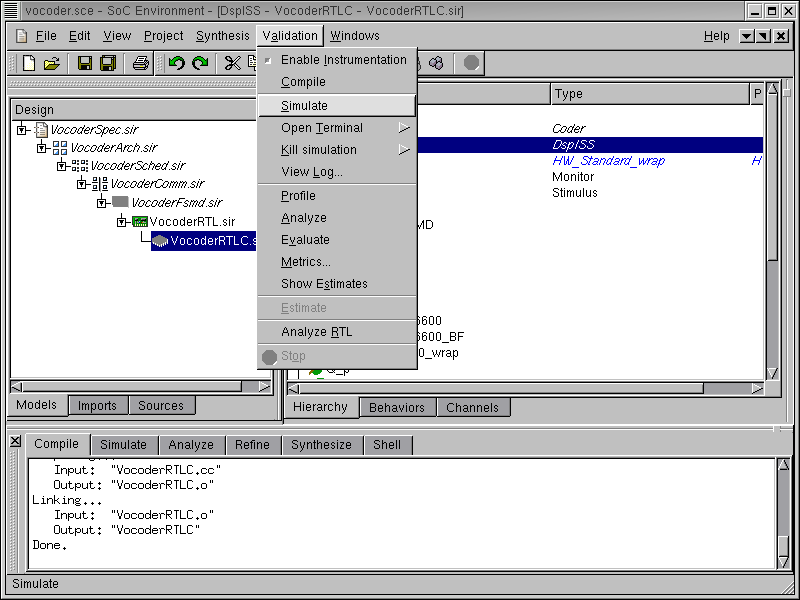

We now have the clock cycle accurate model ready for validation. We begin as usual with compiling the model by selecting Validation->Compile from the menu bar.

5.3.2.1. Simulate cycle accurate model (cont'd)

The model compiles correctly as shown in the logging window. We now proceed to simulate the model by selecting Validation->Simulate from the menu bar.

5.3.2.2. Simulate cycle accurate model (cont'd)

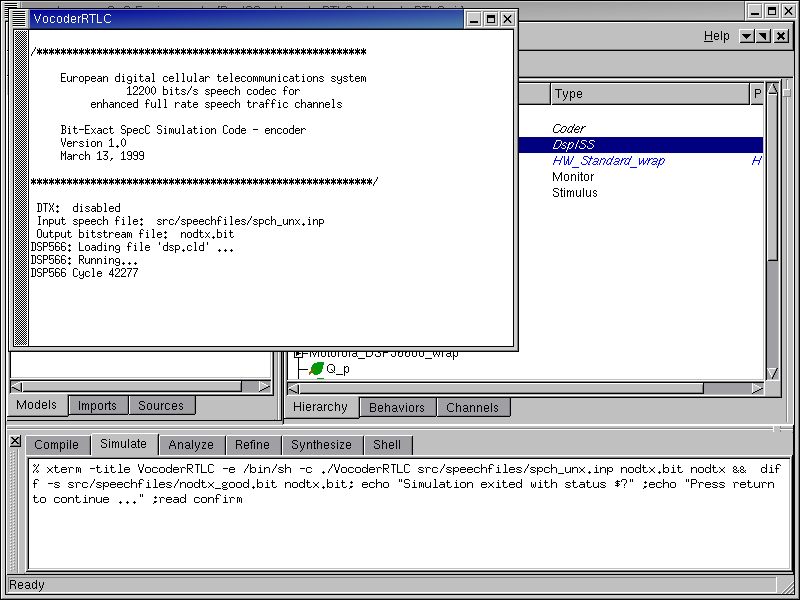

Like in the earlier cases, a simulation window pops up. The DSP Instruction set simulator can be seen to slow down the simulation speed considerably. This is because the simulation is being done one instruction at a time in contrast to the high level simulation we had earlier.

5.3.2.3. Simulate cycle accurate model (cont'd)

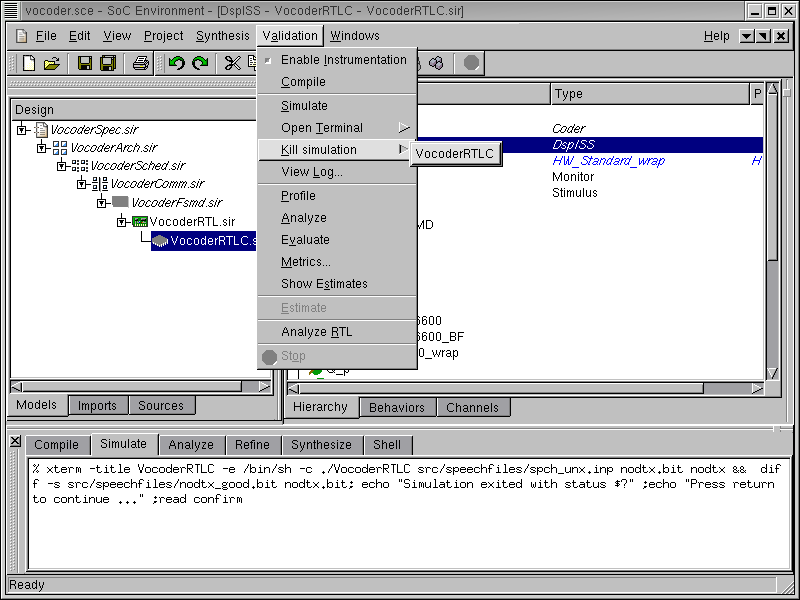

It may take hours for the simulation to complete. The simulation may be killed by selecting Validation->Kill simulation from the menu bar.

5.3.2.4. Simulate cycle accurate model (cont'd)

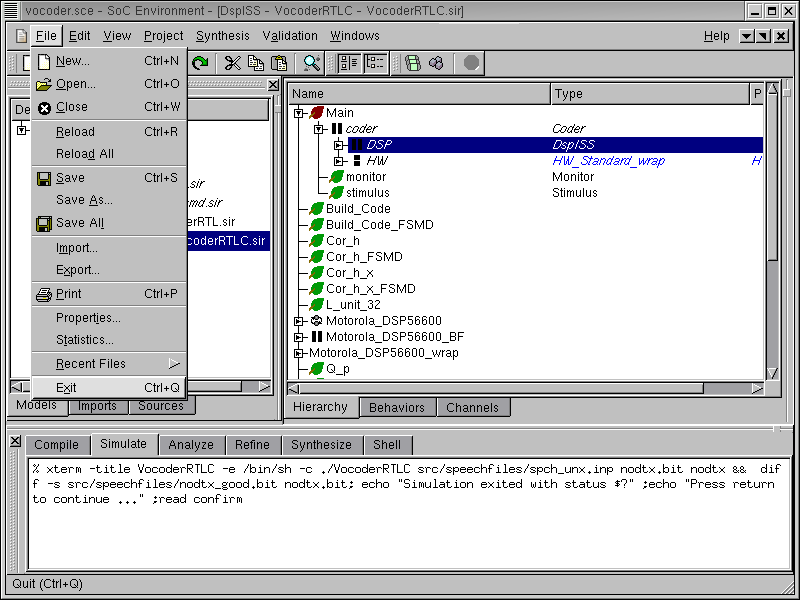

The demo has now concluded. To exit the SoC environment, select Project->Exit from the menu bar.