5.2. SW code generation

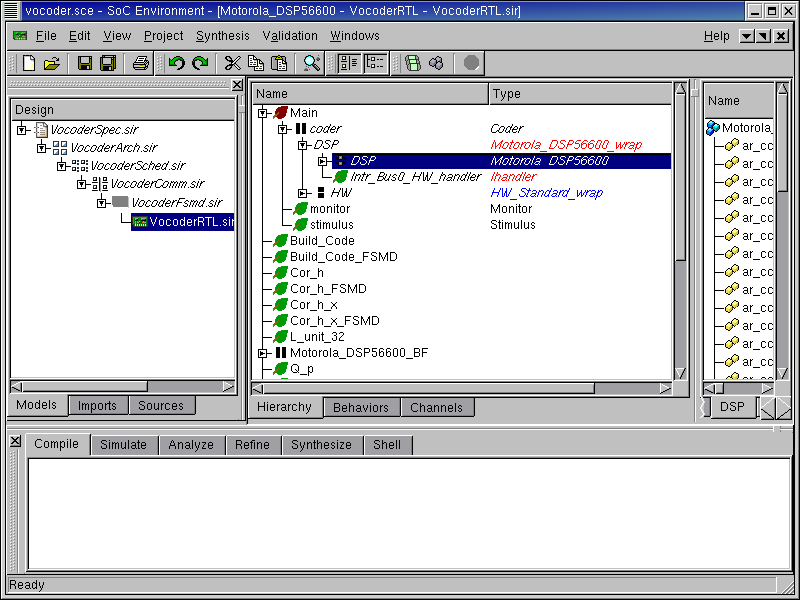

Once we are done with HW and have obtained a RTL model, we will generate software for the DSP. For our design example, we need to generate C code for behavior "Motorola_DSP56600" and all its child behaviors. We start by selecting behavior "Motorola_DSP56600" in the design hierarchy tree.

5.2.1. Generate C code

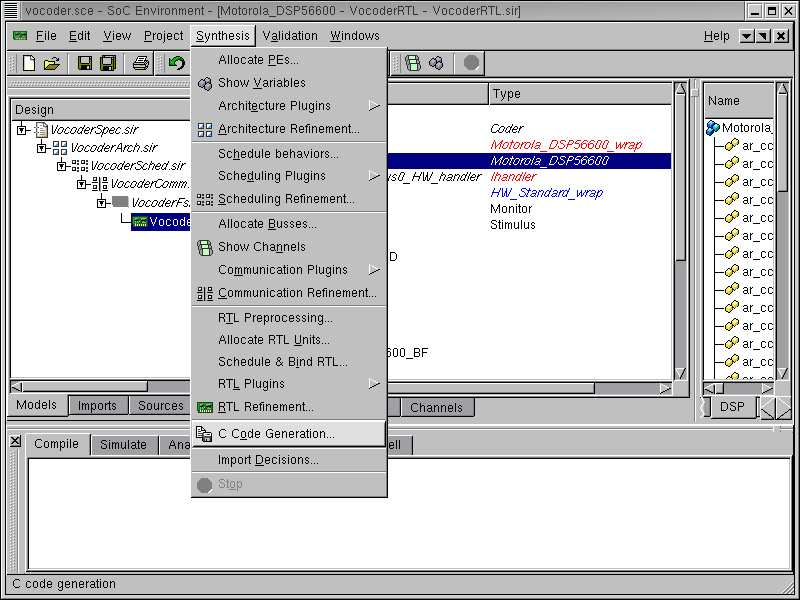

To generate C code for behavior "Motorola_DSP56600", select Synthesis->C Code Generation... from the menu bar.

5.2.1.1. Generate C code (cont'd)

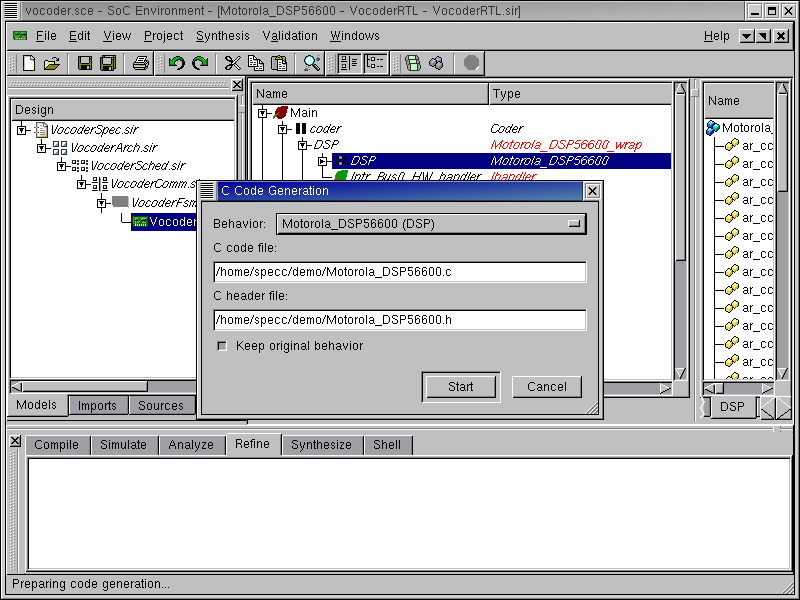

A dialog box pops up for the user to input the name of the C and Header file of the generated software. Now press the Start button to start the C code generation process.

5.2.1.2. Generate C code (cont'd)

As displayed in the logging window, the software generation is being performed. The newly generated software model "VocoderRTL.C.sir" is displayed to the design window. It is also added to the current project window, under the RTL model "VocoderRTL.sir" to indicate that it was derived from "VocoderRTL.sir"

5.2.1.3. Generate C code (cont'd)

Like in the previous sections, we need to change the design name to follow the same naming style in this tutorial. In the project window, select design "VocoderRTL.C.sir". Right click and select Rename... Change the design name to "VocoderRTLC.sir"

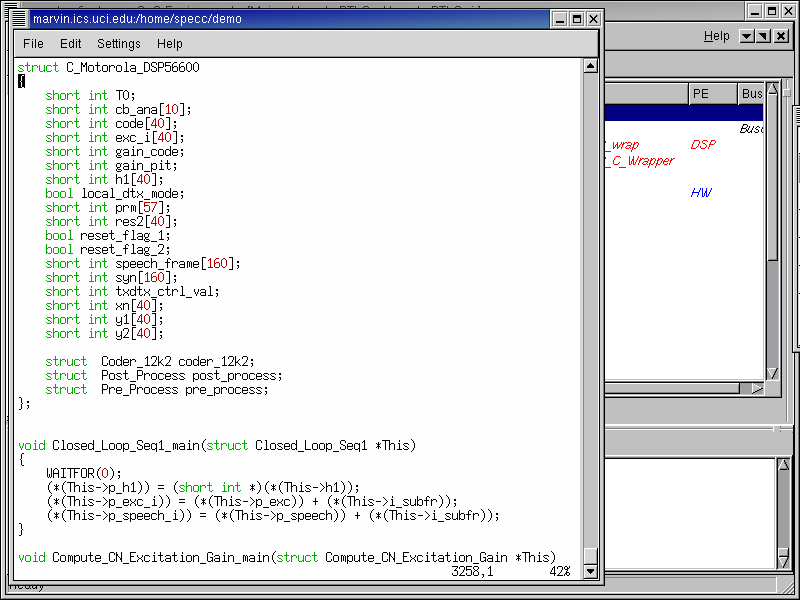

5.2.2. Browse and View C code

Check out the C code generated in the file "Motorola_DSP56600.c". This code is generated by the software generation tool. The designer may go to the shell and launch his favorite editor to browse through the generated C code.

The code generation process converts the SpecC description of tasks into ANSI C code. The main idea is that we convert the behaviors and channels into C struct and convert the behavioral hierarchy into the C struct hierarchy. Variables defined inside a behavior or channel and ports of behaviors are converted into data members of the corresponding C struct. Finally, functions inside a behavior or channel are converted into global functions with an additional parameter added representing the behavior to which the function belongs.

5.2.3. Simulate C model (optional)

So far we have finished the C code generation. However, we also need to confirm that the generated C code is correct for the design. In other words the C code must be functionally equivalent to the SpecC model. The simulation step is optional, so if the designer is not interested in it, he or she may skip it and go directly to Section 5.3.

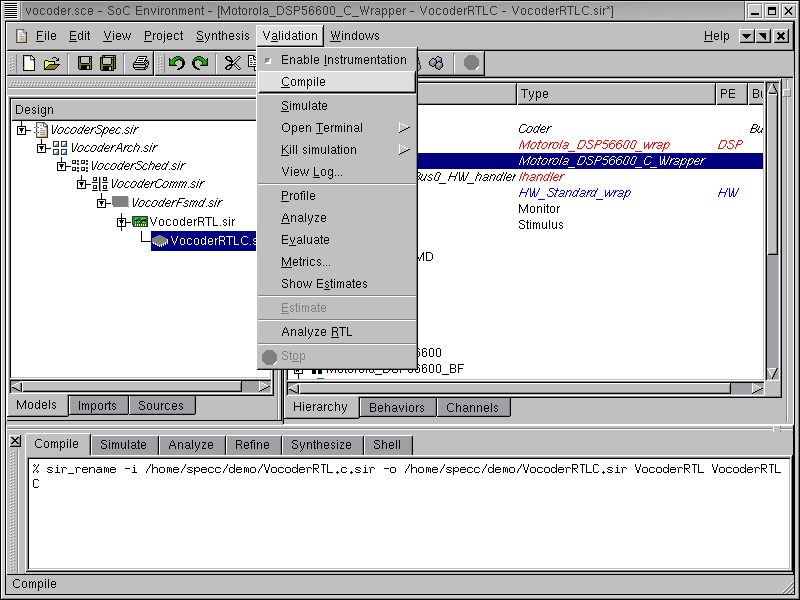

We will validate the generated C code through simulation. But first we need to import C code into the design and compile the model into an executable. To compile the C code model to executable, go to Validation menu and select Compile .

5.2.3.1. Simulate C model (cont'd)

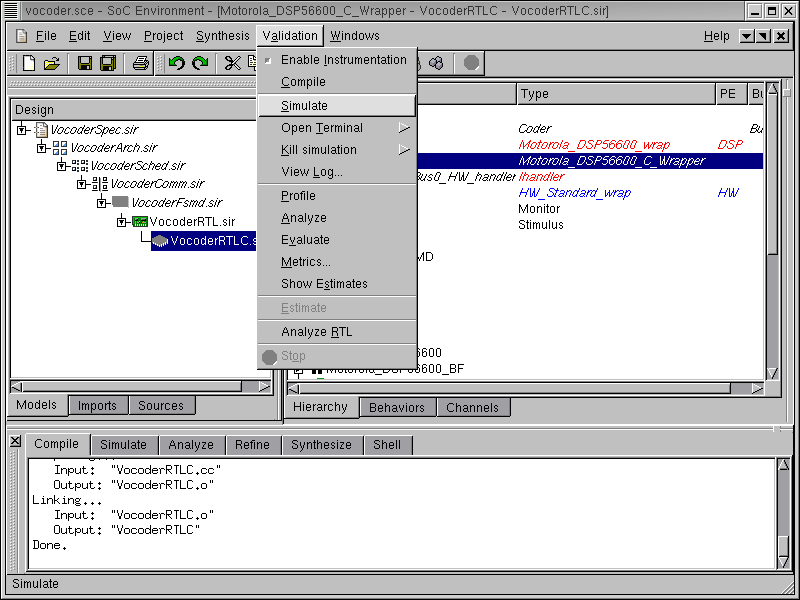

The messages in the logging window shows that the C code model is compiled successfully without any syntax errors. Now in order to verify that it is functionally equivalent to the previous model, we will simulate the compiled model on the same set of speech data used in the specification validation. Go to Validation menu and select Simulate .

5.2.3.2. Simulate C model (cont'd)

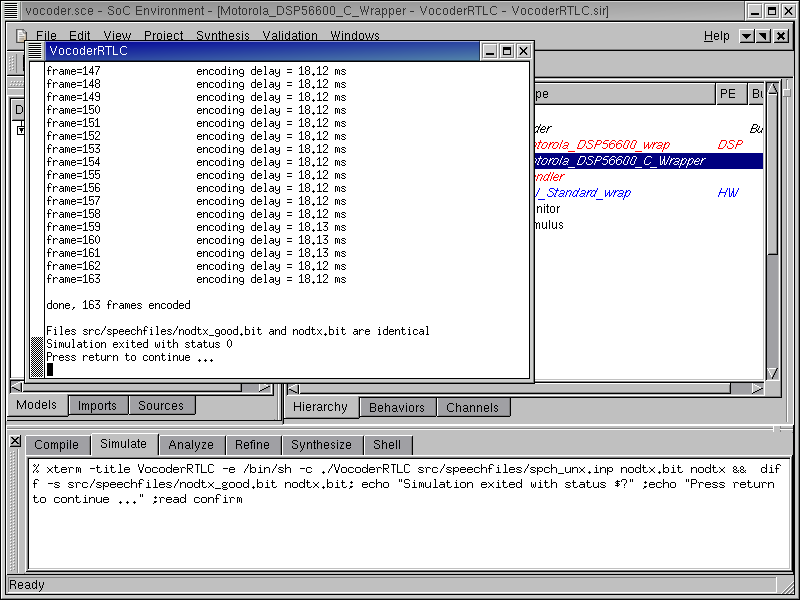

Like in the earlier cases, a simulation window pops up. The simulation result is correct and we have thus verified that the generated C code is functionally correct.