Chapter 5. Embedded Software Design

5.1. Overview

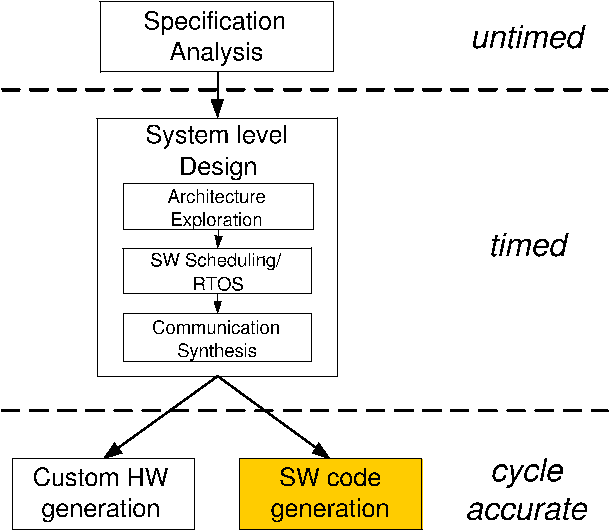

In this chapter, we look at software code generation as highlighted in Figure 5-1. The bus functional model derived after system level design contains a behavioral hierarchy of tasks mapped to SW components. Since the SpecC code is not a natural input for generating the processor's instruction-set specific code, we need to produce C code that can be compiled for the processor. In this phase we use the SW generation tool to flatten the hierarchical SpecC code and produce C code. We thus enable the designer to use an off the shelf processor with C compiler and produce cycle accurate SW for it. The instruction set simulator for the processor can be used in conjunction with the SpecC simulator to perform cycle accurate simulation of both HW and SW.