Chapter 3. System Level Design

3.1. Overview

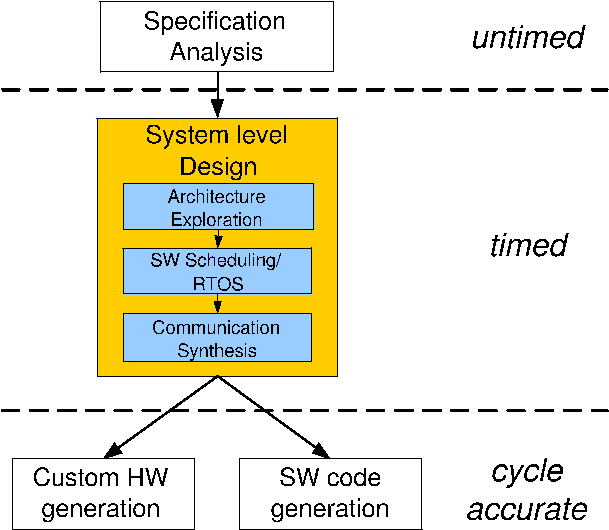

System design is increasingly being performed at higher levels of abstraction to deal with a variety of issues. In this chapter, we look at system level design tasks with SCE as highlighted in Figure 3-1. Firstly, we need to deal with both HW and SW in a single model. Secondly, and more importantly, complexity becomes unmanageable. In this chapter we will look at the system level design phase as shown in the above figure. This phase comprises of architecture exploration, serialization/RTOS insertion and communication synthesis. Architecture exploration deals with coming up with a suitable system architecture and distributing the system tasks in the specification onto those components. Since each component has a single control, we need to serialize the tasks in each component. Tasks that are mapped to SW can be dynamically scheduled on the processor by inserting an RTOS model. Finally, we perform communication synthesis to come up with a communication architecture and refine the data transfer and interfaces to use the communication architecture. The goal of this phase is to come up with a model that can serve as an input to RTL synthesis for HW components and SW generation for processors.