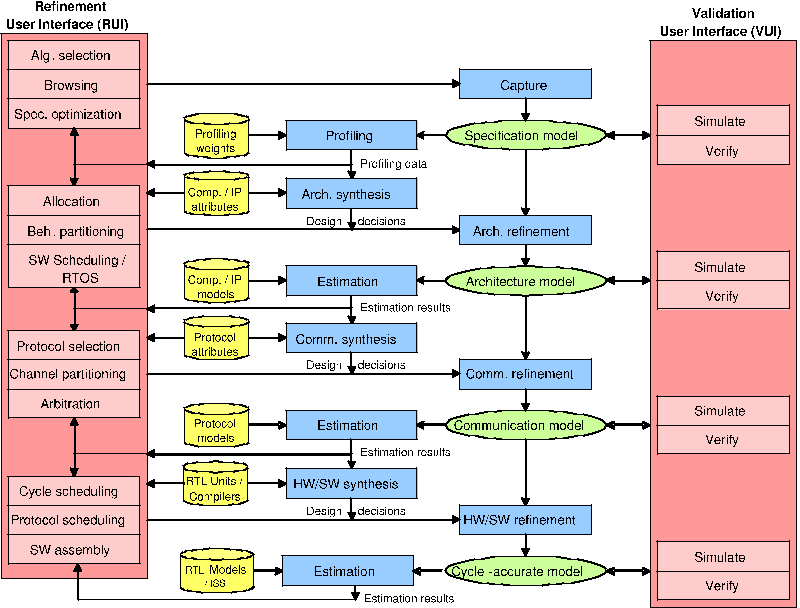

1.3. Models for System Design

The System-on-Chip design environment is shown in Figure 1-1. It consists of 4 levels of model abstraction, namely specification, architecture, communication and cycle-accurate models. Consequently, there are 3 refinement steps, namely architecture refinement, communication refinement and HW/SW refinement. These refinement steps are preformed in the top-down order as shown. As shown in Figure 1-1, we begin with an abstract specification model. The specification model is untimed and has only the functional description of the design. Architecture refinement transforms this specification to an architecture model. It involves partitioning the design and mapping the partitions onto the selected components. The architecture model thus reflects the intended architecture for the design. The next step, communication refinement, adds system busses to the design and maps the abstract communication between components onto the busses. The resulted design is a timing accurate communication model (bus functional model). The final step is HW/SW refinement which produces clock cycle accurate RTL model for the hardware components and instruction set specific assembly code for the processors. All models have well defined semantics, are executable and can be validated through simulation.