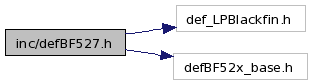

#include <def_LPBlackfin.h>#include <defBF52x_base.h>Include dependency graph for defBF527.h:

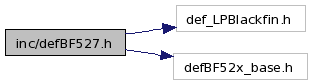

This graph shows which files directly or indirectly include this file:

Defines | |

| #define | EMAC_OPMODE 0xFFC03000 |

| #define | EMAC_ADDRLO 0xFFC03004 |

| #define | EMAC_ADDRHI 0xFFC03008 |

| #define | EMAC_HASHLO 0xFFC0300C |

| #define | EMAC_HASHHI 0xFFC03010 |

| #define | EMAC_STAADD 0xFFC03014 |

| #define | EMAC_STADAT 0xFFC03018 |

| #define | EMAC_FLC 0xFFC0301C |

| #define | EMAC_VLAN1 0xFFC03020 |

| #define | EMAC_VLAN2 0xFFC03024 |

| #define | EMAC_WKUP_CTL 0xFFC0302C |

| #define | EMAC_WKUP_FFMSK0 0xFFC03030 |

| #define | EMAC_WKUP_FFMSK1 0xFFC03034 |

| #define | EMAC_WKUP_FFMSK2 0xFFC03038 |

| #define | EMAC_WKUP_FFMSK3 0xFFC0303C |

| #define | EMAC_WKUP_FFCMD 0xFFC03040 |

| #define | EMAC_WKUP_FFOFF 0xFFC03044 |

| #define | EMAC_WKUP_FFCRC0 0xFFC03048 |

| #define | EMAC_WKUP_FFCRC1 0xFFC0304C |

| #define | EMAC_SYSCTL 0xFFC03060 |

| #define | EMAC_SYSTAT 0xFFC03064 |

| #define | EMAC_RX_STAT 0xFFC03068 |

| #define | EMAC_RX_STKY 0xFFC0306C |

| #define | EMAC_RX_IRQE 0xFFC03070 |

| #define | EMAC_TX_STAT 0xFFC03074 |

| #define | EMAC_TX_STKY 0xFFC03078 |

| #define | EMAC_TX_IRQE 0xFFC0307C |

| #define | EMAC_MMC_CTL 0xFFC03080 |

| #define | EMAC_MMC_RIRQS 0xFFC03084 |

| #define | EMAC_MMC_RIRQE 0xFFC03088 |

| #define | EMAC_MMC_TIRQS 0xFFC0308C |

| #define | EMAC_MMC_TIRQE 0xFFC03090 |

| #define | EMAC_RXC_OK 0xFFC03100 |

| #define | EMAC_RXC_FCS 0xFFC03104 |

| #define | EMAC_RXC_ALIGN 0xFFC03108 |

| #define | EMAC_RXC_OCTET 0xFFC0310C |

| #define | EMAC_RXC_DMAOVF 0xFFC03110 |

| #define | EMAC_RXC_UNICST 0xFFC03114 |

| #define | EMAC_RXC_MULTI 0xFFC03118 |

| #define | EMAC_RXC_BROAD 0xFFC0311C |

| #define | EMAC_RXC_LNERRI 0xFFC03120 |

| #define | EMAC_RXC_LNERRO 0xFFC03124 |

| #define | EMAC_RXC_LONG 0xFFC03128 |

| #define | EMAC_RXC_MACCTL 0xFFC0312C |

| #define | EMAC_RXC_OPCODE 0xFFC03130 |

| #define | EMAC_RXC_PAUSE 0xFFC03134 |

| #define | EMAC_RXC_ALLFRM 0xFFC03138 |

| #define | EMAC_RXC_ALLOCT 0xFFC0313C |

| #define | EMAC_RXC_TYPED 0xFFC03140 |

| #define | EMAC_RXC_SHORT 0xFFC03144 |

| #define | EMAC_RXC_EQ64 0xFFC03148 |

| #define | EMAC_RXC_LT128 0xFFC0314C |

| #define | EMAC_RXC_LT256 0xFFC03150 |

| #define | EMAC_RXC_LT512 0xFFC03154 |

| #define | EMAC_RXC_LT1024 0xFFC03158 |

| #define | EMAC_RXC_GE1024 0xFFC0315C |

| #define | EMAC_TXC_OK 0xFFC03180 |

| #define | EMAC_TXC_1COL 0xFFC03184 |

| #define | EMAC_TXC_GT1COL 0xFFC03188 |

| #define | EMAC_TXC_OCTET 0xFFC0318C |

| #define | EMAC_TXC_DEFER 0xFFC03190 |

| #define | EMAC_TXC_LATECL 0xFFC03194 |

| #define | EMAC_TXC_XS_COL 0xFFC03198 |

| #define | EMAC_TXC_DMAUND 0xFFC0319C |

| #define | EMAC_TXC_CRSERR 0xFFC031A0 |

| #define | EMAC_TXC_UNICST 0xFFC031A4 |

| #define | EMAC_TXC_MULTI 0xFFC031A8 |

| #define | EMAC_TXC_BROAD 0xFFC031AC |

| #define | EMAC_TXC_XS_DFR 0xFFC031B0 |

| #define | EMAC_TXC_MACCTL 0xFFC031B4 |

| #define | EMAC_TXC_ALLFRM 0xFFC031B8 |

| #define | EMAC_TXC_ALLOCT 0xFFC031BC |

| #define | EMAC_TXC_EQ64 0xFFC031C0 |

| #define | EMAC_TXC_LT128 0xFFC031C4 |

| #define | EMAC_TXC_LT256 0xFFC031C8 |

| #define | EMAC_TXC_LT512 0xFFC031CC |

| #define | EMAC_TXC_LT1024 0xFFC031D0 |

| #define | EMAC_TXC_GE1024 0xFFC031D4 |

| #define | EMAC_TXC_ABORT 0xFFC031D8 |

| #define | FramesReceivedOK EMAC_RXC_OK |

| #define | FrameCheckSequenceErrors EMAC_RXC_FCS |

| #define | AlignmentErrors EMAC_RXC_ALIGN |

| #define | OctetsReceivedOK EMAC_RXC_OCTET |

| #define | FramesLostDueToIntMACRcvError EMAC_RXC_DMAOVF |

| #define | UnicastFramesReceivedOK EMAC_RXC_UNICST |

| #define | MulticastFramesReceivedOK EMAC_RXC_MULTI |

| #define | BroadcastFramesReceivedOK EMAC_RXC_BROAD |

| #define | InRangeLengthErrors EMAC_RXC_LNERRI |

| #define | OutOfRangeLengthField EMAC_RXC_LNERRO |

| #define | FrameTooLongErrors EMAC_RXC_LONG |

| #define | MACControlFramesReceived EMAC_RXC_MACCTL |

| #define | UnsupportedOpcodesReceived EMAC_RXC_OPCODE |

| #define | PAUSEMACCtrlFramesReceived EMAC_RXC_PAUSE |

| #define | FramesReceivedAll EMAC_RXC_ALLFRM |

| #define | OctetsReceivedAll EMAC_RXC_ALLOCT |

| #define | TypedFramesReceived EMAC_RXC_TYPED |

| #define | FramesLenLt64Received EMAC_RXC_SHORT |

| #define | FramesLenEq64Received EMAC_RXC_EQ64 |

| #define | FramesLen65_127Received EMAC_RXC_LT128 |

| #define | FramesLen128_255Received EMAC_RXC_LT256 |

| #define | FramesLen256_511Received EMAC_RXC_LT512 |

| #define | FramesLen512_1023Received EMAC_RXC_LT1024 |

| #define | FramesLen1024_MaxReceived EMAC_RXC_GE1024 |

| #define | FramesTransmittedOK EMAC_TXC_OK |

| #define | SingleCollisionFrames EMAC_TXC_1COL |

| #define | MultipleCollisionFrames EMAC_TXC_GT1COL |

| #define | OctetsTransmittedOK EMAC_TXC_OCTET |

| #define | FramesWithDeferredXmissions EMAC_TXC_DEFER |

| #define | LateCollisions EMAC_TXC_LATECL |

| #define | FramesAbortedDueToXSColls EMAC_TXC_XS_COL |

| #define | FramesLostDueToIntMacXmitError EMAC_TXC_DMAUND |

| #define | CarrierSenseErrors EMAC_TXC_CRSERR |

| #define | UnicastFramesXmittedOK EMAC_TXC_UNICST |

| #define | MulticastFramesXmittedOK EMAC_TXC_MULTI |

| #define | BroadcastFramesXmittedOK EMAC_TXC_BROAD |

| #define | FramesWithExcessiveDeferral EMAC_TXC_XS_DFR |

| #define | MACControlFramesTransmitted EMAC_TXC_MACCTL |

| #define | FramesTransmittedAll EMAC_TXC_ALLFRM |

| #define | OctetsTransmittedAll EMAC_TXC_ALLOCT |

| #define | FramesLenEq64Transmitted EMAC_TXC_EQ64 |

| #define | FramesLen65_127Transmitted EMAC_TXC_LT128 |

| #define | FramesLen128_255Transmitted EMAC_TXC_LT256 |

| #define | FramesLen256_511Transmitted EMAC_TXC_LT512 |

| #define | FramesLen512_1023Transmitted EMAC_TXC_LT1024 |

| #define | FramesLen1024_MaxTransmitted EMAC_TXC_GE1024 |

| #define | TxAbortedFrames EMAC_TXC_ABORT |

| #define | RE 0x00000001 |

| #define | ASTP 0x00000002 |

| #define | HU 0x00000010 |

| #define | HM 0x00000020 |

| #define | PAM 0x00000040 |

| #define | PR 0x00000080 |

| #define | IFE 0x00000100 |

| #define | DBF 0x00000200 |

| #define | PBF 0x00000400 |

| #define | PSF 0x00000800 |

| #define | RAF 0x00001000 |

| #define | TE 0x00010000 |

| #define | DTXPAD 0x00020000 |

| #define | DTXCRC 0x00040000 |

| #define | DC 0x00080000 |

| #define | BOLMT 0x00300000 |

| #define | BOLMT_10 0x00000000 |

| #define | BOLMT_8 0x00100000 |

| #define | BOLMT_4 0x00200000 |

| #define | BOLMT_1 0x00300000 |

| #define | DRTY 0x00400000 |

| #define | LCTRE 0x00800000 |

| #define | RMII 0x01000000 |

| #define | RMII_10 0x02000000 |

| #define | FDMODE 0x04000000 |

| #define | LB 0x08000000 |

| #define | DRO 0x10000000 |

| #define | STABUSY 0x00000001 |

| #define | STAOP 0x00000002 |

| #define | STADISPRE 0x00000004 |

| #define | STAIE 0x00000008 |

| #define | REGAD 0x000007C0 |

| #define | PHYAD 0x0000F800 |

| #define | SET_REGAD(x) (((x)&0x1F)<< 6 ) |

| #define | SET_PHYAD(x) (((x)&0x1F)<< 11 ) |

| #define | STADATA 0x0000FFFF |

| #define | FLCBUSY 0x00000001 |

| #define | FLCE 0x00000002 |

| #define | PCF 0x00000004 |

| #define | BKPRSEN 0x00000008 |

| #define | FLCPAUSE 0xFFFF0000 |

| #define | SET_FLCPAUSE(x) (((x)&0xFFFF)<< 16) |

| #define | CAPWKFRM 0x00000001 |

| #define | MPKE 0x00000002 |

| #define | RWKE 0x00000004 |

| #define | GUWKE 0x00000008 |

| #define | MPKS 0x00000020 |

| #define | RWKS 0x00000F00 |

| #define | WF0_E 0x00000001 |

| #define | WF0_T 0x00000008 |

| #define | WF1_E 0x00000100 |

| #define | WF1_T 0x00000800 |

| #define | WF2_E 0x00010000 |

| #define | WF2_T 0x00080000 |

| #define | WF3_E 0x01000000 |

| #define | WF3_T 0x08000000 |

| #define | WF0_OFF 0x000000FF |

| #define | WF1_OFF 0x0000FF00 |

| #define | WF2_OFF 0x00FF0000 |

| #define | WF3_OFF 0xFF000000 |

| #define | SET_WF0_OFF(x) (((x)&0xFF)<< 0 ) |

| #define | SET_WF1_OFF(x) (((x)&0xFF)<< 8 ) |

| #define | SET_WF2_OFF(x) (((x)&0xFF)<< 16 ) |

| #define | SET_WF3_OFF(x) (((x)&0xFF)<< 24 ) |

| #define | SET_WF_OFFS(x0, x1, x2, x3) (SET_WF0_OFF((x0))|SET_WF1_OFF((x1))|SET_WF2_OFF((x2))|SET_WF3_OFF((x3))) |

| #define | WF0_CRC 0x0000FFFF |

| #define | WF1_CRC 0xFFFF0000 |

| #define | SET_WF0_CRC(x) (((x)&0xFFFF)<< 0 ) |

| #define | SET_WF1_CRC(x) (((x)&0xFFFF)<< 16 ) |

| #define | WF2_CRC 0x0000FFFF |

| #define | WF3_CRC 0xFFFF0000 |

| #define | SET_WF2_CRC(x) (((x)&0xFFFF)<< 0 ) |

| #define | SET_WF3_CRC(x) (((x)&0xFFFF)<< 16 ) |

| #define | PHYIE 0x00000001 |

| #define | RXDWA 0x00000002 |

| #define | RXCKS 0x00000004 |

| #define | MDCDIV 0x00003F00 |

| #define | SET_MDCDIV(x) (((x)&0x3F)<< 8) |

| #define | PHYINT 0x00000001 |

| #define | MMCINT 0x00000002 |

| #define | RXFSINT 0x00000004 |

| #define | TXFSINT 0x00000008 |

| #define | WAKEDET 0x00000010 |

| #define | RXDMAERR 0x00000020 |

| #define | TXDMAERR 0x00000040 |

| #define | STMDONE 0x00000080 |

| #define | RX_FRLEN 0x000007FF |

| #define | RX_COMP 0x00001000 |

| #define | RX_OK 0x00002000 |

| #define | RX_LONG 0x00004000 |

| #define | RX_ALIGN 0x00008000 |

| #define | RX_CRC 0x00010000 |

| #define | RX_LEN 0x00020000 |

| #define | RX_FRAG 0x00040000 |

| #define | RX_ADDR 0x00080000 |

| #define | RX_DMAO 0x00100000 |

| #define | RX_PHY 0x00200000 |

| #define | RX_LATE 0x00400000 |

| #define | RX_RANGE 0x00800000 |

| #define | RX_MULTI 0x01000000 |

| #define | RX_BROAD 0x02000000 |

| #define | RX_CTL 0x04000000 |

| #define | RX_UCTL 0x08000000 |

| #define | RX_TYPE 0x10000000 |

| #define | RX_VLAN1 0x20000000 |

| #define | RX_VLAN2 0x40000000 |

| #define | RX_ACCEPT 0x80000000 |

| #define | TX_COMP 0x00000001 |

| #define | TX_OK 0x00000002 |

| #define | TX_ECOLL 0x00000004 |

| #define | TX_LATE 0x00000008 |

| #define | TX_DMAU 0x00000010 |

| #define | TX_MACE 0x00000010 |

| #define | TX_EDEFER 0x00000020 |

| #define | TX_BROAD 0x00000040 |

| #define | TX_MULTI 0x00000080 |

| #define | TX_CCNT 0x00000F00 |

| #define | TX_DEFER 0x00001000 |

| #define | TX_CRS 0x00002000 |

| #define | TX_LOSS 0x00004000 |

| #define | TX_RETRY 0x00008000 |

| #define | TX_FRLEN 0x07FF0000 |

| #define | RSTC 0x00000001 |

| #define | CROLL 0x00000002 |

| #define | CCOR 0x00000004 |

| #define | MMCE 0x00000008 |

| #define | RX_OK_CNT 0x00000001 |

| #define | RX_FCS_CNT 0x00000002 |

| #define | RX_ALIGN_CNT 0x00000004 |

| #define | RX_OCTET_CNT 0x00000008 |

| #define | RX_LOST_CNT 0x00000010 |

| #define | RX_UNI_CNT 0x00000020 |

| #define | RX_MULTI_CNT 0x00000040 |

| #define | RX_BROAD_CNT 0x00000080 |

| #define | RX_IRL_CNT 0x00000100 |

| #define | RX_ORL_CNT 0x00000200 |

| #define | RX_LONG_CNT 0x00000400 |

| #define | RX_MACCTL_CNT 0x00000800 |

| #define | RX_OPCODE_CTL 0x00001000 |

| #define | RX_PAUSE_CNT 0x00002000 |

| #define | RX_ALLF_CNT 0x00004000 |

| #define | RX_ALLO_CNT 0x00008000 |

| #define | RX_TYPED_CNT 0x00010000 |

| #define | RX_SHORT_CNT 0x00020000 |

| #define | RX_EQ64_CNT 0x00040000 |

| #define | RX_LT128_CNT 0x00080000 |

| #define | RX_LT256_CNT 0x00100000 |

| #define | RX_LT512_CNT 0x00200000 |

| #define | RX_LT1024_CNT 0x00400000 |

| #define | RX_GE1024_CNT 0x00800000 |

| #define | TX_OK_CNT 0x00000001 |

| #define | TX_SCOLL_CNT 0x00000002 |

| #define | TX_MCOLL_CNT 0x00000004 |

| #define | TX_OCTET_CNT 0x00000008 |

| #define | TX_DEFER_CNT 0x00000010 |

| #define | TX_LATE_CNT 0x00000020 |

| #define | TX_ABORTC_CNT 0x00000040 |

| #define | TX_LOST_CNT 0x00000080 |

| #define | TX_CRS_CNT 0x00000100 |

| #define | TX_UNI_CNT 0x00000200 |

| #define | TX_MULTI_CNT 0x00000400 |

| #define | TX_BROAD_CNT 0x00000800 |

| #define | TX_EXDEF_CTL 0x00001000 |

| #define | TX_MACCTL_CNT 0x00002000 |

| #define | TX_ALLF_CNT 0x00004000 |

| #define | TX_ALLO_CNT 0x00008000 |

| #define | TX_EQ64_CNT 0x00010000 |

| #define | TX_LT128_CNT 0x00020000 |

| #define | TX_LT256_CNT 0x00040000 |

| #define | TX_LT512_CNT 0x00080000 |

| #define | TX_LT1024_CNT 0x00100000 |

| #define | TX_GE1024_CNT 0x00200000 |

| #define | TX_ABORT_CNT 0x00400000 |

| #define | USB_FADDR 0xffc03800 |

| #define | USB_POWER 0xffc03804 |

| #define | USB_INTRTX 0xffc03808 |

| #define | USB_INTRRX 0xffc0380c |

| #define | USB_INTRTXE 0xffc03810 |

| #define | USB_INTRRXE 0xffc03814 |

| #define | USB_INTRUSB 0xffc03818 |

| #define | USB_INTRUSBE 0xffc0381c |

| #define | USB_FRAME 0xffc03820 |

| #define | USB_INDEX 0xffc03824 |

| #define | USB_TESTMODE 0xffc03828 |

| #define | USB_GLOBINTR 0xffc0382c |

| #define | USB_GLOBAL_CTL 0xffc03830 |

| #define | USB_TX_MAX_PACKET 0xffc03840 |

| #define | USB_CSR0 0xffc03844 |

| #define | USB_TXCSR 0xffc03844 |

| #define | USB_RX_MAX_PACKET 0xffc03848 |

| #define | USB_RXCSR 0xffc0384c |

| #define | USB_COUNT0 0xffc03850 |

| #define | USB_RXCOUNT 0xffc03850 |

| #define | USB_TXTYPE 0xffc03854 |

| #define | USB_NAKLIMIT0 0xffc03858 |

| #define | USB_TXINTERVAL 0xffc03858 |

| #define | USB_RXTYPE 0xffc0385c |

| #define | USB_RXINTERVAL 0xffc03860 |

| #define | USB_TXCOUNT 0xffc03868 |

| #define | USB_EP0_FIFO 0xffc03880 |

| #define | USB_EP1_FIFO 0xffc03888 |

| #define | USB_EP2_FIFO 0xffc03890 |

| #define | USB_EP3_FIFO 0xffc03898 |

| #define | USB_EP4_FIFO 0xffc038a0 |

| #define | USB_EP5_FIFO 0xffc038a8 |

| #define | USB_EP6_FIFO 0xffc038b0 |

| #define | USB_EP7_FIFO 0xffc038b8 |

| #define | USB_OTG_DEV_CTL 0xffc03900 |

| #define | USB_OTG_VBUS_IRQ 0xffc03904 |

| #define | USB_OTG_VBUS_MASK 0xffc03908 |

| #define | USB_LINKINFO 0xffc03948 |

| #define | USB_VPLEN 0xffc0394c |

| #define | USB_HS_EOF1 0xffc03950 |

| #define | USB_FS_EOF1 0xffc03954 |

| #define | USB_LS_EOF1 0xffc03958 |

| #define | USB_APHY_CNTRL 0xffc039e0 |

| #define | USB_APHY_CALIB 0xffc039e4 |

| #define | USB_APHY_CNTRL2 0xffc039e8 |

| #define | USB_PHY_TEST 0xffc039ec |

| #define | USB_PLLOSC_CTRL 0xffc039f0 |

| #define | USB_SRP_CLKDIV 0xffc039f4 |

| #define | USB_EP_NI0_TXMAXP 0xffc03a00 |

| #define | USB_EP_NI0_TXCSR 0xffc03a04 |

| #define | USB_EP_NI0_RXMAXP 0xffc03a08 |

| #define | USB_EP_NI0_RXCSR 0xffc03a0c |

| #define | USB_EP_NI0_RXCOUNT 0xffc03a10 |

| #define | USB_EP_NI0_TXTYPE 0xffc03a14 |

| #define | USB_EP_NI0_TXINTERVAL 0xffc03a18 |

| #define | USB_EP_NI0_RXTYPE 0xffc03a1c |

| #define | USB_EP_NI0_RXINTERVAL 0xffc03a20 |

| #define | USB_EP_NI0_TXCOUNT 0xffc03a28 |

| #define | USB_EP_NI1_TXMAXP 0xffc03a40 |

| #define | USB_EP_NI1_TXCSR 0xffc03a44 |

| #define | USB_EP_NI1_RXMAXP 0xffc03a48 |

| #define | USB_EP_NI1_RXCSR 0xffc03a4c |

| #define | USB_EP_NI1_RXCOUNT 0xffc03a50 |

| #define | USB_EP_NI1_TXTYPE 0xffc03a54 |

| #define | USB_EP_NI1_TXINTERVAL 0xffc03a58 |

| #define | USB_EP_NI1_RXTYPE 0xffc03a5c |

| #define | USB_EP_NI1_RXINTERVAL 0xffc03a60 |

| #define | USB_EP_NI1_TXCOUNT 0xffc03a68 |

| #define | USB_EP_NI2_TXMAXP 0xffc03a80 |

| #define | USB_EP_NI2_TXCSR 0xffc03a84 |

| #define | USB_EP_NI2_RXMAXP 0xffc03a88 |

| #define | USB_EP_NI2_RXCSR 0xffc03a8c |

| #define | USB_EP_NI2_RXCOUNT 0xffc03a90 |

| #define | USB_EP_NI2_TXTYPE 0xffc03a94 |

| #define | USB_EP_NI2_TXINTERVAL 0xffc03a98 |

| #define | USB_EP_NI2_RXTYPE 0xffc03a9c |

| #define | USB_EP_NI2_RXINTERVAL 0xffc03aa0 |

| #define | USB_EP_NI2_TXCOUNT 0xffc03aa8 |

| #define | USB_EP_NI3_TXMAXP 0xffc03ac0 |

| #define | USB_EP_NI3_TXCSR 0xffc03ac4 |

| #define | USB_EP_NI3_RXMAXP 0xffc03ac8 |

| #define | USB_EP_NI3_RXCSR 0xffc03acc |

| #define | USB_EP_NI3_RXCOUNT 0xffc03ad0 |

| #define | USB_EP_NI3_TXTYPE 0xffc03ad4 |

| #define | USB_EP_NI3_TXINTERVAL 0xffc03ad8 |

| #define | USB_EP_NI3_RXTYPE 0xffc03adc |

| #define | USB_EP_NI3_RXINTERVAL 0xffc03ae0 |

| #define | USB_EP_NI3_TXCOUNT 0xffc03ae8 |

| #define | USB_EP_NI4_TXMAXP 0xffc03b00 |

| #define | USB_EP_NI4_TXCSR 0xffc03b04 |

| #define | USB_EP_NI4_RXMAXP 0xffc03b08 |

| #define | USB_EP_NI4_RXCSR 0xffc03b0c |

| #define | USB_EP_NI4_RXCOUNT 0xffc03b10 |

| #define | USB_EP_NI4_TXTYPE 0xffc03b14 |

| #define | USB_EP_NI4_TXINTERVAL 0xffc03b18 |

| #define | USB_EP_NI4_RXTYPE 0xffc03b1c |

| #define | USB_EP_NI4_RXINTERVAL 0xffc03b20 |

| #define | USB_EP_NI4_TXCOUNT 0xffc03b28 |

| #define | USB_EP_NI5_TXMAXP 0xffc03b40 |

| #define | USB_EP_NI5_TXCSR 0xffc03b44 |

| #define | USB_EP_NI5_RXMAXP 0xffc03b48 |

| #define | USB_EP_NI5_RXCSR 0xffc03b4c |

| #define | USB_EP_NI5_RXCOUNT 0xffc03b50 |

| #define | USB_EP_NI5_TXTYPE 0xffc03b54 |

| #define | USB_EP_NI5_TXINTERVAL 0xffc03b58 |

| #define | USB_EP_NI5_RXTYPE 0xffc03b5c |

| #define | USB_EP_NI5_RXINTERVAL 0xffc03b60 |

| #define | USB_EP_NI5_TXCOUNT 0xffc03b68 |

| #define | USB_EP_NI6_TXMAXP 0xffc03b80 |

| #define | USB_EP_NI6_TXCSR 0xffc03b84 |

| #define | USB_EP_NI6_RXMAXP 0xffc03b88 |

| #define | USB_EP_NI6_RXCSR 0xffc03b8c |

| #define | USB_EP_NI6_RXCOUNT 0xffc03b90 |

| #define | USB_EP_NI6_TXTYPE 0xffc03b94 |

| #define | USB_EP_NI6_TXINTERVAL 0xffc03b98 |

| #define | USB_EP_NI6_RXTYPE 0xffc03b9c |

| #define | USB_EP_NI6_RXINTERVAL 0xffc03ba0 |

| #define | USB_EP_NI6_TXCOUNT 0xffc03ba8 |

| #define | USB_EP_NI7_TXMAXP 0xffc03bc0 |

| #define | USB_EP_NI7_TXCSR 0xffc03bc4 |

| #define | USB_EP_NI7_RXMAXP 0xffc03bc8 |

| #define | USB_EP_NI7_RXCSR 0xffc03bcc |

| #define | USB_EP_NI7_RXCOUNT 0xffc03bd0 |

| #define | USB_EP_NI7_TXTYPE 0xffc03bd4 |

| #define | USB_EP_NI7_TXINTERVAL 0xffc03bd8 |

| #define | USB_EP_NI7_RXTYPE 0xffc03bdc |

| #define | USB_EP_NI7_RXINTERVAL 0xffc03bf0 |

| #define | USB_EP_NI7_TXCOUNT 0xffc03bf8 |

| #define | USB_DMA_INTERRUPT 0xffc03c00 |

| #define | USB_DMA0CONTROL 0xffc03c04 |

| #define | USB_DMA0ADDRLOW 0xffc03c08 |

| #define | USB_DMA0ADDRHIGH 0xffc03c0c |

| #define | USB_DMA0COUNTLOW 0xffc03c10 |

| #define | USB_DMA0COUNTHIGH 0xffc03c14 |

| #define | USB_DMA1CONTROL 0xffc03c24 |

| #define | USB_DMA1ADDRLOW 0xffc03c28 |

| #define | USB_DMA1ADDRHIGH 0xffc03c2c |

| #define | USB_DMA1COUNTLOW 0xffc03c30 |

| #define | USB_DMA1COUNTHIGH 0xffc03c34 |

| #define | USB_DMA2CONTROL 0xffc03c44 |

| #define | USB_DMA2ADDRLOW 0xffc03c48 |

| #define | USB_DMA2ADDRHIGH 0xffc03c4c |

| #define | USB_DMA2COUNTLOW 0xffc03c50 |

| #define | USB_DMA2COUNTHIGH 0xffc03c54 |

| #define | USB_DMA3CONTROL 0xffc03c64 |

| #define | USB_DMA3ADDRLOW 0xffc03c68 |

| #define | USB_DMA3ADDRHIGH 0xffc03c6c |

| #define | USB_DMA3COUNTLOW 0xffc03c70 |

| #define | USB_DMA3COUNTHIGH 0xffc03c74 |

| #define | USB_DMA4CONTROL 0xffc03c84 |

| #define | USB_DMA4ADDRLOW 0xffc03c88 |

| #define | USB_DMA4ADDRHIGH 0xffc03c8c |

| #define | USB_DMA4COUNTLOW 0xffc03c90 |

| #define | USB_DMA4COUNTHIGH 0xffc03c94 |

| #define | USB_DMA5CONTROL 0xffc03ca4 |

| #define | USB_DMA5ADDRLOW 0xffc03ca8 |

| #define | USB_DMA5ADDRHIGH 0xffc03cac |

| #define | USB_DMA5COUNTLOW 0xffc03cb0 |

| #define | USB_DMA5COUNTHIGH 0xffc03cb4 |

| #define | USB_DMA6CONTROL 0xffc03cc4 |

| #define | USB_DMA6ADDRLOW 0xffc03cc8 |

| #define | USB_DMA6ADDRHIGH 0xffc03ccc |

| #define | USB_DMA6COUNTLOW 0xffc03cd0 |

| #define | USB_DMA6COUNTHIGH 0xffc03cd4 |

| #define | USB_DMA7CONTROL 0xffc03ce4 |

| #define | USB_DMA7ADDRLOW 0xffc03ce8 |

| #define | USB_DMA7ADDRHIGH 0xffc03cec |

| #define | USB_DMA7COUNTLOW 0xffc03cf0 |

| #define | USB_DMA7COUNTHIGH 0xffc03cf4 |

| #define | FUNCTION_ADDRESS 0x7f |

| #define | ENABLE_SUSPENDM 0x1 |

| #define | nENABLE_SUSPENDM 0x0 |

| #define | SUSPEND_MODE 0x2 |

| #define | nSUSPEND_MODE 0x0 |

| #define | RESUME_MODE 0x4 |

| #define | nRESUME_MODE 0x0 |

| #define | RESET 0x8 |

| #define | nRESET 0x0 |

| #define | HS_MODE 0x10 |

| #define | nHS_MODE 0x0 |

| #define | HS_ENABLE 0x20 |

| #define | nHS_ENABLE 0x0 |

| #define | SOFT_CONN 0x40 |

| #define | nSOFT_CONN 0x0 |

| #define | ISO_UPDATE 0x80 |

| #define | nISO_UPDATE 0x0 |

| #define | EP0_TX 0x1 |

| #define | nEP0_TX 0x0 |

| #define | EP1_TX 0x2 |

| #define | nEP1_TX 0x0 |

| #define | EP2_TX 0x4 |

| #define | nEP2_TX 0x0 |

| #define | EP3_TX 0x8 |

| #define | nEP3_TX 0x0 |

| #define | EP4_TX 0x10 |

| #define | nEP4_TX 0x0 |

| #define | EP5_TX 0x20 |

| #define | nEP5_TX 0x0 |

| #define | EP6_TX 0x40 |

| #define | nEP6_TX 0x0 |

| #define | EP7_TX 0x80 |

| #define | nEP7_TX 0x0 |

| #define | EP1_RX 0x2 |

| #define | nEP1_RX 0x0 |

| #define | EP2_RX 0x4 |

| #define | nEP2_RX 0x0 |

| #define | EP3_RX 0x8 |

| #define | nEP3_RX 0x0 |

| #define | EP4_RX 0x10 |

| #define | nEP4_RX 0x0 |

| #define | EP5_RX 0x20 |

| #define | nEP5_RX 0x0 |

| #define | EP6_RX 0x40 |

| #define | nEP6_RX 0x0 |

| #define | EP7_RX 0x80 |

| #define | nEP7_RX 0x0 |

| #define | EP0_TX_E 0x1 |

| #define | nEP0_TX_E 0x0 |

| #define | EP1_TX_E 0x2 |

| #define | nEP1_TX_E 0x0 |

| #define | EP2_TX_E 0x4 |

| #define | nEP2_TX_E 0x0 |

| #define | EP3_TX_E 0x8 |

| #define | nEP3_TX_E 0x0 |

| #define | EP4_TX_E 0x10 |

| #define | nEP4_TX_E 0x0 |

| #define | EP5_TX_E 0x20 |

| #define | nEP5_TX_E 0x0 |

| #define | EP6_TX_E 0x40 |

| #define | nEP6_TX_E 0x0 |

| #define | EP7_TX_E 0x80 |

| #define | nEP7_TX_E 0x0 |

| #define | EP1_RX_E 0x2 |

| #define | nEP1_RX_E 0x0 |

| #define | EP2_RX_E 0x4 |

| #define | nEP2_RX_E 0x0 |

| #define | EP3_RX_E 0x8 |

| #define | nEP3_RX_E 0x0 |

| #define | EP4_RX_E 0x10 |

| #define | nEP4_RX_E 0x0 |

| #define | EP5_RX_E 0x20 |

| #define | nEP5_RX_E 0x0 |

| #define | EP6_RX_E 0x40 |

| #define | nEP6_RX_E 0x0 |

| #define | EP7_RX_E 0x80 |

| #define | nEP7_RX_E 0x0 |

| #define | SUSPEND_B 0x1 |

| #define | nSUSPEND_B 0x0 |

| #define | RESUME_B 0x2 |

| #define | nRESUME_B 0x0 |

| #define | RESET_OR_BABLE_B 0x4 |

| #define | nRESET_OR_BABLE_B 0x0 |

| #define | SOF_B 0x8 |

| #define | nSOF_B 0x0 |

| #define | CONN_B 0x10 |

| #define | nCONN_B 0x0 |

| #define | DISCON_B 0x20 |

| #define | nDISCON_B 0x0 |

| #define | SESSION_REQ_B 0x40 |

| #define | nSESSION_REQ_B 0x0 |

| #define | VBUS_ERROR_B 0x80 |

| #define | nVBUS_ERROR_B 0x0 |

| #define | SUSPEND_BE 0x1 |

| #define | nSUSPEND_BE 0x0 |

| #define | RESUME_BE 0x2 |

| #define | nRESUME_BE 0x0 |

| #define | RESET_OR_BABLE_BE 0x4 |

| #define | nRESET_OR_BABLE_BE 0x0 |

| #define | SOF_BE 0x8 |

| #define | nSOF_BE 0x0 |

| #define | CONN_BE 0x10 |

| #define | nCONN_BE 0x0 |

| #define | DISCON_BE 0x20 |

| #define | nDISCON_BE 0x0 |

| #define | SESSION_REQ_BE 0x40 |

| #define | nSESSION_REQ_BE 0x0 |

| #define | VBUS_ERROR_BE 0x80 |

| #define | nVBUS_ERROR_BE 0x0 |

| #define | FRAME_NUMBER 0x7ff |

| #define | SELECTED_ENDPOINT 0xf |

| #define | GLOBAL_ENA 0x1 |

| #define | nGLOBAL_ENA 0x0 |

| #define | EP1_TX_ENA 0x2 |

| #define | nEP1_TX_ENA 0x0 |

| #define | EP2_TX_ENA 0x4 |

| #define | nEP2_TX_ENA 0x0 |

| #define | EP3_TX_ENA 0x8 |

| #define | nEP3_TX_ENA 0x0 |

| #define | EP4_TX_ENA 0x10 |

| #define | nEP4_TX_ENA 0x0 |

| #define | EP5_TX_ENA 0x20 |

| #define | nEP5_TX_ENA 0x0 |

| #define | EP6_TX_ENA 0x40 |

| #define | nEP6_TX_ENA 0x0 |

| #define | EP7_TX_ENA 0x80 |

| #define | nEP7_TX_ENA 0x0 |

| #define | EP1_RX_ENA 0x100 |

| #define | nEP1_RX_ENA 0x0 |

| #define | EP2_RX_ENA 0x200 |

| #define | nEP2_RX_ENA 0x0 |

| #define | EP3_RX_ENA 0x400 |

| #define | nEP3_RX_ENA 0x0 |

| #define | EP4_RX_ENA 0x800 |

| #define | nEP4_RX_ENA 0x0 |

| #define | EP5_RX_ENA 0x1000 |

| #define | nEP5_RX_ENA 0x0 |

| #define | EP6_RX_ENA 0x2000 |

| #define | nEP6_RX_ENA 0x0 |

| #define | EP7_RX_ENA 0x4000 |

| #define | nEP7_RX_ENA 0x0 |

| #define | SESSION 0x1 |

| #define | nSESSION 0x0 |

| #define | HOST_REQ 0x2 |

| #define | nHOST_REQ 0x0 |

| #define | HOST_MODE 0x4 |

| #define | nHOST_MODE 0x0 |

| #define | VBUS0 0x8 |

| #define | nVBUS0 0x0 |

| #define | VBUS1 0x10 |

| #define | nVBUS1 0x0 |

| #define | LSDEV 0x20 |

| #define | nLSDEV 0x0 |

| #define | FSDEV 0x40 |

| #define | nFSDEV 0x0 |

| #define | B_DEVICE 0x80 |

| #define | nB_DEVICE 0x0 |

| #define | DRIVE_VBUS_ON 0x1 |

| #define | nDRIVE_VBUS_ON 0x0 |

| #define | DRIVE_VBUS_OFF 0x2 |

| #define | nDRIVE_VBUS_OFF 0x0 |

| #define | CHRG_VBUS_START 0x4 |

| #define | nCHRG_VBUS_START 0x0 |

| #define | CHRG_VBUS_END 0x8 |

| #define | nCHRG_VBUS_END 0x0 |

| #define | DISCHRG_VBUS_START 0x10 |

| #define | nDISCHRG_VBUS_START 0x0 |

| #define | DISCHRG_VBUS_END 0x20 |

| #define | nDISCHRG_VBUS_END 0x0 |

| #define | DRIVE_VBUS_ON_ENA 0x1 |

| #define | nDRIVE_VBUS_ON_ENA 0x0 |

| #define | DRIVE_VBUS_OFF_ENA 0x2 |

| #define | nDRIVE_VBUS_OFF_ENA 0x0 |

| #define | CHRG_VBUS_START_ENA 0x4 |

| #define | nCHRG_VBUS_START_ENA 0x0 |

| #define | CHRG_VBUS_END_ENA 0x8 |

| #define | nCHRG_VBUS_END_ENA 0x0 |

| #define | DISCHRG_VBUS_START_ENA 0x10 |

| #define | nDISCHRG_VBUS_START_ENA 0x0 |

| #define | DISCHRG_VBUS_END_ENA 0x20 |

| #define | nDISCHRG_VBUS_END_ENA 0x0 |

| #define | RXPKTRDY 0x1 |

| #define | nRXPKTRDY 0x0 |

| #define | TXPKTRDY 0x2 |

| #define | nTXPKTRDY 0x0 |

| #define | STALL_SENT 0x4 |

| #define | nSTALL_SENT 0x0 |

| #define | DATAEND 0x8 |

| #define | nDATAEND 0x0 |

| #define | SETUPEND 0x10 |

| #define | nSETUPEND 0x0 |

| #define | SENDSTALL 0x20 |

| #define | nSENDSTALL 0x0 |

| #define | SERVICED_RXPKTRDY 0x40 |

| #define | nSERVICED_RXPKTRDY 0x0 |

| #define | SERVICED_SETUPEND 0x80 |

| #define | nSERVICED_SETUPEND 0x0 |

| #define | FLUSHFIFO 0x100 |

| #define | nFLUSHFIFO 0x0 |

| #define | STALL_RECEIVED_H 0x4 |

| #define | nSTALL_RECEIVED_H 0x0 |

| #define | SETUPPKT_H 0x8 |

| #define | nSETUPPKT_H 0x0 |

| #define | ERROR_H 0x10 |

| #define | nERROR_H 0x0 |

| #define | REQPKT_H 0x20 |

| #define | nREQPKT_H 0x0 |

| #define | STATUSPKT_H 0x40 |

| #define | nSTATUSPKT_H 0x0 |

| #define | NAK_TIMEOUT_H 0x80 |

| #define | nNAK_TIMEOUT_H 0x0 |

| #define | EP0_RX_COUNT 0x7f |

| #define | EP0_NAK_LIMIT 0x1f |

| #define | MAX_PACKET_SIZE_T 0x7ff |

| #define | MAX_PACKET_SIZE_R 0x7ff |

| #define | TXPKTRDY_T 0x1 |

| #define | nTXPKTRDY_T 0x0 |

| #define | FIFO_NOT_EMPTY_T 0x2 |

| #define | nFIFO_NOT_EMPTY_T 0x0 |

| #define | UNDERRUN_T 0x4 |

| #define | nUNDERRUN_T 0x0 |

| #define | FLUSHFIFO_T 0x8 |

| #define | nFLUSHFIFO_T 0x0 |

| #define | STALL_SEND_T 0x10 |

| #define | nSTALL_SEND_T 0x0 |

| #define | STALL_SENT_T 0x20 |

| #define | nSTALL_SENT_T 0x0 |

| #define | CLEAR_DATATOGGLE_T 0x40 |

| #define | nCLEAR_DATATOGGLE_T 0x0 |

| #define | INCOMPTX_T 0x80 |

| #define | nINCOMPTX_T 0x0 |

| #define | DMAREQMODE_T 0x400 |

| #define | nDMAREQMODE_T 0x0 |

| #define | FORCE_DATATOGGLE_T 0x800 |

| #define | nFORCE_DATATOGGLE_T 0x0 |

| #define | DMAREQ_ENA_T 0x1000 |

| #define | nDMAREQ_ENA_T 0x0 |

| #define | ISO_T 0x4000 |

| #define | nISO_T 0x0 |

| #define | AUTOSET_T 0x8000 |

| #define | nAUTOSET_T 0x0 |

| #define | ERROR_TH 0x4 |

| #define | nERROR_TH 0x0 |

| #define | STALL_RECEIVED_TH 0x20 |

| #define | nSTALL_RECEIVED_TH 0x0 |

| #define | NAK_TIMEOUT_TH 0x80 |

| #define | nNAK_TIMEOUT_TH 0x0 |

| #define | TX_COUNT 0x1fff |

| #define | RXPKTRDY_R 0x1 |

| #define | nRXPKTRDY_R 0x0 |

| #define | FIFO_FULL_R 0x2 |

| #define | nFIFO_FULL_R 0x0 |

| #define | OVERRUN_R 0x4 |

| #define | nOVERRUN_R 0x0 |

| #define | DATAERROR_R 0x8 |

| #define | nDATAERROR_R 0x0 |

| #define | FLUSHFIFO_R 0x10 |

| #define | nFLUSHFIFO_R 0x0 |

| #define | STALL_SEND_R 0x20 |

| #define | nSTALL_SEND_R 0x0 |

| #define | STALL_SENT_R 0x40 |

| #define | nSTALL_SENT_R 0x0 |

| #define | CLEAR_DATATOGGLE_R 0x80 |

| #define | nCLEAR_DATATOGGLE_R 0x0 |

| #define | INCOMPRX_R 0x100 |

| #define | nINCOMPRX_R 0x0 |

| #define | DMAREQMODE_R 0x800 |

| #define | nDMAREQMODE_R 0x0 |

| #define | DISNYET_R 0x1000 |

| #define | nDISNYET_R 0x0 |

| #define | DMAREQ_ENA_R 0x2000 |

| #define | nDMAREQ_ENA_R 0x0 |

| #define | ISO_R 0x4000 |

| #define | nISO_R 0x0 |

| #define | AUTOCLEAR_R 0x8000 |

| #define | nAUTOCLEAR_R 0x0 |

| #define | ERROR_RH 0x4 |

| #define | nERROR_RH 0x0 |

| #define | REQPKT_RH 0x20 |

| #define | nREQPKT_RH 0x0 |

| #define | STALL_RECEIVED_RH 0x40 |

| #define | nSTALL_RECEIVED_RH 0x0 |

| #define | INCOMPRX_RH 0x100 |

| #define | nINCOMPRX_RH 0x0 |

| #define | DMAREQMODE_RH 0x800 |

| #define | nDMAREQMODE_RH 0x0 |

| #define | AUTOREQ_RH 0x4000 |

| #define | nAUTOREQ_RH 0x0 |

| #define | RX_COUNT 0x1fff |

| #define | TARGET_EP_NO_T 0xf |

| #define | PROTOCOL_T 0xc |

| #define | TX_POLL_INTERVAL 0xff |

| #define | TARGET_EP_NO_R 0xf |

| #define | PROTOCOL_R 0xc |

| #define | RX_POLL_INTERVAL 0xff |

| #define | DMA0_INT 0x1 |

| #define | nDMA0_INT 0x0 |

| #define | DMA1_INT 0x2 |

| #define | nDMA1_INT 0x0 |

| #define | DMA2_INT 0x4 |

| #define | nDMA2_INT 0x0 |

| #define | DMA3_INT 0x8 |

| #define | nDMA3_INT 0x0 |

| #define | DMA4_INT 0x10 |

| #define | nDMA4_INT 0x0 |

| #define | DMA5_INT 0x20 |

| #define | nDMA5_INT 0x0 |

| #define | DMA6_INT 0x40 |

| #define | nDMA6_INT 0x0 |

| #define | DMA7_INT 0x80 |

| #define | nDMA7_INT 0x0 |

| #define | DMA_ENA 0x1 |

| #define | nDMA_ENA 0x0 |

| #define | DIRECTION 0x2 |

| #define | nDIRECTION 0x0 |

| #define | MODE 0x4 |

| #define | nMODE 0x0 |

| #define | INT_ENA 0x8 |

| #define | nINT_ENA 0x0 |

| #define | EPNUM 0xf0 |

| #define | BUSERROR 0x100 |

| #define | nBUSERROR 0x0 |

| #define | DMA_ADDR_HIGH 0xffff |

| #define | DMA_ADDR_LOW 0xffff |

| #define | DMA_COUNT_HIGH 0xffff |

| #define | DMA_COUNT_LOW 0xffff |

| #define AlignmentErrors EMAC_RXC_ALIGN |

| #define ASTP 0x00000002 |

| #define AUTOCLEAR_R 0x8000 |

| #define AUTOREQ_RH 0x4000 |

| #define AUTOSET_T 0x8000 |

| #define B_DEVICE 0x80 |

| #define BKPRSEN 0x00000008 |

| #define BOLMT 0x00300000 |

| #define BOLMT_1 0x00300000 |

| #define BOLMT_10 0x00000000 |

| #define BOLMT_4 0x00200000 |

| #define BOLMT_8 0x00100000 |

| #define BroadcastFramesReceivedOK EMAC_RXC_BROAD |

| #define BroadcastFramesXmittedOK EMAC_TXC_BROAD |

| #define BUSERROR 0x100 |

| #define CAPWKFRM 0x00000001 |

| #define CarrierSenseErrors EMAC_TXC_CRSERR |

| #define CCOR 0x00000004 |

| #define CHRG_VBUS_END 0x8 |

| #define CHRG_VBUS_END_ENA 0x8 |

| #define CHRG_VBUS_START 0x4 |

| #define CHRG_VBUS_START_ENA 0x4 |

| #define CLEAR_DATATOGGLE_R 0x80 |

| #define CLEAR_DATATOGGLE_T 0x40 |

| #define CONN_B 0x10 |

| #define CONN_BE 0x10 |

| #define CROLL 0x00000002 |

| #define DATAEND 0x8 |

| #define DATAERROR_R 0x8 |

| #define DBF 0x00000200 |

| #define DC 0x00080000 |

| #define DIRECTION 0x2 |

| #define DISCHRG_VBUS_END 0x20 |

| #define DISCHRG_VBUS_END_ENA 0x20 |

| #define DISCHRG_VBUS_START 0x10 |

| #define DISCHRG_VBUS_START_ENA 0x10 |

| #define DISCON_B 0x20 |

| #define DISCON_BE 0x20 |

| #define DISNYET_R 0x1000 |

| #define DMA0_INT 0x1 |

| #define DMA1_INT 0x2 |

| #define DMA2_INT 0x4 |

| #define DMA3_INT 0x8 |

| #define DMA4_INT 0x10 |

| #define DMA5_INT 0x20 |

| #define DMA6_INT 0x40 |

| #define DMA7_INT 0x80 |

| #define DMA_ADDR_HIGH 0xffff |

| #define DMA_ADDR_LOW 0xffff |

| #define DMA_COUNT_HIGH 0xffff |

| #define DMA_COUNT_LOW 0xffff |

| #define DMA_ENA 0x1 |

| #define DMAREQ_ENA_R 0x2000 |

| #define DMAREQ_ENA_T 0x1000 |

| #define DMAREQMODE_R 0x800 |

| #define DMAREQMODE_RH 0x800 |

| #define DMAREQMODE_T 0x400 |

| #define DRIVE_VBUS_OFF 0x2 |

| #define DRIVE_VBUS_OFF_ENA 0x2 |

| #define DRIVE_VBUS_ON 0x1 |

| #define DRIVE_VBUS_ON_ENA 0x1 |

| #define DRO 0x10000000 |

| #define DRTY 0x00400000 |

| #define DTXCRC 0x00040000 |

| #define DTXPAD 0x00020000 |

| #define EMAC_ADDRHI 0xFFC03008 |

| #define EMAC_ADDRLO 0xFFC03004 |

| #define EMAC_FLC 0xFFC0301C |

| #define EMAC_HASHHI 0xFFC03010 |

| #define EMAC_HASHLO 0xFFC0300C |

| #define EMAC_MMC_CTL 0xFFC03080 |

| #define EMAC_MMC_RIRQE 0xFFC03088 |

| #define EMAC_MMC_RIRQS 0xFFC03084 |

| #define EMAC_MMC_TIRQE 0xFFC03090 |

| #define EMAC_MMC_TIRQS 0xFFC0308C |

| #define EMAC_OPMODE 0xFFC03000 |

| #define EMAC_RX_IRQE 0xFFC03070 |

| #define EMAC_RX_STAT 0xFFC03068 |

| #define EMAC_RX_STKY 0xFFC0306C |

| #define EMAC_RXC_ALIGN 0xFFC03108 |

| #define EMAC_RXC_ALLFRM 0xFFC03138 |

| #define EMAC_RXC_ALLOCT 0xFFC0313C |

| #define EMAC_RXC_BROAD 0xFFC0311C |

| #define EMAC_RXC_DMAOVF 0xFFC03110 |

| #define EMAC_RXC_EQ64 0xFFC03148 |

| #define EMAC_RXC_FCS 0xFFC03104 |

| #define EMAC_RXC_GE1024 0xFFC0315C |

| #define EMAC_RXC_LNERRI 0xFFC03120 |

| #define EMAC_RXC_LNERRO 0xFFC03124 |

| #define EMAC_RXC_LONG 0xFFC03128 |

| #define EMAC_RXC_LT1024 0xFFC03158 |

| #define EMAC_RXC_LT128 0xFFC0314C |

| #define EMAC_RXC_LT256 0xFFC03150 |

| #define EMAC_RXC_LT512 0xFFC03154 |

| #define EMAC_RXC_MACCTL 0xFFC0312C |

| #define EMAC_RXC_MULTI 0xFFC03118 |

| #define EMAC_RXC_OCTET 0xFFC0310C |

| #define EMAC_RXC_OK 0xFFC03100 |

| #define EMAC_RXC_OPCODE 0xFFC03130 |

| #define EMAC_RXC_PAUSE 0xFFC03134 |

| #define EMAC_RXC_SHORT 0xFFC03144 |

| #define EMAC_RXC_TYPED 0xFFC03140 |

| #define EMAC_RXC_UNICST 0xFFC03114 |

| #define EMAC_STAADD 0xFFC03014 |

| #define EMAC_STADAT 0xFFC03018 |

| #define EMAC_SYSCTL 0xFFC03060 |

| #define EMAC_SYSTAT 0xFFC03064 |

| #define EMAC_TX_IRQE 0xFFC0307C |

| #define EMAC_TX_STAT 0xFFC03074 |

| #define EMAC_TX_STKY 0xFFC03078 |

| #define EMAC_TXC_1COL 0xFFC03184 |

| #define EMAC_TXC_ABORT 0xFFC031D8 |

| #define EMAC_TXC_ALLFRM 0xFFC031B8 |

| #define EMAC_TXC_ALLOCT 0xFFC031BC |

| #define EMAC_TXC_BROAD 0xFFC031AC |

| #define EMAC_TXC_CRSERR 0xFFC031A0 |

| #define EMAC_TXC_DEFER 0xFFC03190 |

| #define EMAC_TXC_DMAUND 0xFFC0319C |

| #define EMAC_TXC_EQ64 0xFFC031C0 |

| #define EMAC_TXC_GE1024 0xFFC031D4 |

| #define EMAC_TXC_GT1COL 0xFFC03188 |

| #define EMAC_TXC_LATECL 0xFFC03194 |

| #define EMAC_TXC_LT1024 0xFFC031D0 |

| #define EMAC_TXC_LT128 0xFFC031C4 |

| #define EMAC_TXC_LT256 0xFFC031C8 |

| #define EMAC_TXC_LT512 0xFFC031CC |

| #define EMAC_TXC_MACCTL 0xFFC031B4 |

| #define EMAC_TXC_MULTI 0xFFC031A8 |

| #define EMAC_TXC_OCTET 0xFFC0318C |

| #define EMAC_TXC_OK 0xFFC03180 |

| #define EMAC_TXC_UNICST 0xFFC031A4 |

| #define EMAC_TXC_XS_COL 0xFFC03198 |

| #define EMAC_TXC_XS_DFR 0xFFC031B0 |

| #define EMAC_VLAN1 0xFFC03020 |

| #define EMAC_VLAN2 0xFFC03024 |

| #define EMAC_WKUP_CTL 0xFFC0302C |

| #define EMAC_WKUP_FFCMD 0xFFC03040 |

| #define EMAC_WKUP_FFCRC0 0xFFC03048 |

| #define EMAC_WKUP_FFCRC1 0xFFC0304C |

| #define EMAC_WKUP_FFMSK0 0xFFC03030 |

| #define EMAC_WKUP_FFMSK1 0xFFC03034 |

| #define EMAC_WKUP_FFMSK2 0xFFC03038 |

| #define EMAC_WKUP_FFMSK3 0xFFC0303C |

| #define EMAC_WKUP_FFOFF 0xFFC03044 |

| #define ENABLE_SUSPENDM 0x1 |

| #define EP0_NAK_LIMIT 0x1f |

| #define EP0_RX_COUNT 0x7f |

| #define EP0_TX 0x1 |

| #define EP0_TX_E 0x1 |

| #define EP1_RX 0x2 |

| #define EP1_RX_E 0x2 |

| #define EP1_RX_ENA 0x100 |

| #define EP1_TX 0x2 |

| #define EP1_TX_E 0x2 |

| #define EP1_TX_ENA 0x2 |

| #define EP2_RX 0x4 |

| #define EP2_RX_E 0x4 |

| #define EP2_RX_ENA 0x200 |

| #define EP2_TX 0x4 |

| #define EP2_TX_E 0x4 |

| #define EP2_TX_ENA 0x4 |

| #define EP3_RX 0x8 |

| #define EP3_RX_E 0x8 |

| #define EP3_RX_ENA 0x400 |

| #define EP3_TX 0x8 |

| #define EP3_TX_E 0x8 |

| #define EP3_TX_ENA 0x8 |

| #define EP4_RX 0x10 |

| #define EP4_RX_E 0x10 |

| #define EP4_RX_ENA 0x800 |

| #define EP4_TX 0x10 |

| #define EP4_TX_E 0x10 |

| #define EP4_TX_ENA 0x10 |

| #define EP5_RX 0x20 |

| #define EP5_RX_E 0x20 |

| #define EP5_RX_ENA 0x1000 |

| #define EP5_TX 0x20 |

| #define EP5_TX_E 0x20 |

| #define EP5_TX_ENA 0x20 |

| #define EP6_RX 0x40 |

| #define EP6_RX_E 0x40 |

| #define EP6_RX_ENA 0x2000 |

| #define EP6_TX 0x40 |

| #define EP6_TX_E 0x40 |

| #define EP6_TX_ENA 0x40 |

| #define EP7_RX 0x80 |

| #define EP7_RX_E 0x80 |

| #define EP7_RX_ENA 0x4000 |

| #define EP7_TX 0x80 |

| #define EP7_TX_E 0x80 |

| #define EP7_TX_ENA 0x80 |

| #define EPNUM 0xf0 |

| #define ERROR_H 0x10 |

| #define ERROR_RH 0x4 |

| #define ERROR_TH 0x4 |

| #define FDMODE 0x04000000 |

| #define FIFO_FULL_R 0x2 |

| #define FIFO_NOT_EMPTY_T 0x2 |

| #define FLCBUSY 0x00000001 |

| #define FLCE 0x00000002 |

| #define FLCPAUSE 0xFFFF0000 |

| #define FLUSHFIFO 0x100 |

| #define FLUSHFIFO_R 0x10 |

| #define FLUSHFIFO_T 0x8 |

| #define FORCE_DATATOGGLE_T 0x800 |

| #define FRAME_NUMBER 0x7ff |

| #define FrameCheckSequenceErrors EMAC_RXC_FCS |

| #define FramesAbortedDueToXSColls EMAC_TXC_XS_COL |

| #define FramesLen1024_MaxReceived EMAC_RXC_GE1024 |

| #define FramesLen1024_MaxTransmitted EMAC_TXC_GE1024 |

| #define FramesLen128_255Received EMAC_RXC_LT256 |

| #define FramesLen128_255Transmitted EMAC_TXC_LT256 |

| #define FramesLen256_511Received EMAC_RXC_LT512 |

| #define FramesLen256_511Transmitted EMAC_TXC_LT512 |

| #define FramesLen512_1023Received EMAC_RXC_LT1024 |

| #define FramesLen512_1023Transmitted EMAC_TXC_LT1024 |

| #define FramesLen65_127Received EMAC_RXC_LT128 |

| #define FramesLen65_127Transmitted EMAC_TXC_LT128 |

| #define FramesLenEq64Received EMAC_RXC_EQ64 |

| #define FramesLenEq64Transmitted EMAC_TXC_EQ64 |

| #define FramesLenLt64Received EMAC_RXC_SHORT |

| #define FramesLostDueToIntMACRcvError EMAC_RXC_DMAOVF |

| #define FramesLostDueToIntMacXmitError EMAC_TXC_DMAUND |

| #define FramesReceivedAll EMAC_RXC_ALLFRM |

| #define FramesReceivedOK EMAC_RXC_OK |

| #define FramesTransmittedAll EMAC_TXC_ALLFRM |

| #define FramesTransmittedOK EMAC_TXC_OK |

| #define FramesWithDeferredXmissions EMAC_TXC_DEFER |

| #define FramesWithExcessiveDeferral EMAC_TXC_XS_DFR |

| #define FrameTooLongErrors EMAC_RXC_LONG |

| #define FSDEV 0x40 |

| #define FUNCTION_ADDRESS 0x7f |

| #define GLOBAL_ENA 0x1 |

| #define GUWKE 0x00000008 |

| #define HM 0x00000020 |

| #define HOST_MODE 0x4 |

| #define HOST_REQ 0x2 |

| #define HS_ENABLE 0x20 |

| #define HS_MODE 0x10 |

| #define HU 0x00000010 |

| #define IFE 0x00000100 |

| #define INCOMPRX_R 0x100 |

| #define INCOMPRX_RH 0x100 |

| #define INCOMPTX_T 0x80 |

| #define InRangeLengthErrors EMAC_RXC_LNERRI |

| #define INT_ENA 0x8 |

| #define ISO_R 0x4000 |

| #define ISO_T 0x4000 |

| #define ISO_UPDATE 0x80 |

| #define LateCollisions EMAC_TXC_LATECL |

| #define LB 0x08000000 |

| #define LCTRE 0x00800000 |

| #define LSDEV 0x20 |

| #define MACControlFramesReceived EMAC_RXC_MACCTL |

| #define MACControlFramesTransmitted EMAC_TXC_MACCTL |

| #define MAX_PACKET_SIZE_R 0x7ff |

| #define MAX_PACKET_SIZE_T 0x7ff |

| #define MDCDIV 0x00003F00 |

| #define MMCE 0x00000008 |

| #define MMCINT 0x00000002 |

| #define MODE 0x4 |

| #define MPKE 0x00000002 |

| #define MPKS 0x00000020 |

| #define MulticastFramesReceivedOK EMAC_RXC_MULTI |

| #define MulticastFramesXmittedOK EMAC_TXC_MULTI |

| #define MultipleCollisionFrames EMAC_TXC_GT1COL |

| #define NAK_TIMEOUT_H 0x80 |

| #define NAK_TIMEOUT_TH 0x80 |

| #define nAUTOCLEAR_R 0x0 |

| #define nAUTOREQ_RH 0x0 |

| #define nAUTOSET_T 0x0 |

| #define nB_DEVICE 0x0 |

| #define nBUSERROR 0x0 |

| #define nCHRG_VBUS_END 0x0 |

| #define nCHRG_VBUS_END_ENA 0x0 |

| #define nCHRG_VBUS_START 0x0 |

| #define nCHRG_VBUS_START_ENA 0x0 |

| #define nCLEAR_DATATOGGLE_R 0x0 |

| #define nCLEAR_DATATOGGLE_T 0x0 |

| #define nCONN_B 0x0 |

| #define nCONN_BE 0x0 |

| #define nDATAEND 0x0 |

| #define nDATAERROR_R 0x0 |

| #define nDIRECTION 0x0 |

| #define nDISCHRG_VBUS_END 0x0 |

| #define nDISCHRG_VBUS_END_ENA 0x0 |

| #define nDISCHRG_VBUS_START 0x0 |

| #define nDISCHRG_VBUS_START_ENA 0x0 |

| #define nDISCON_B 0x0 |

| #define nDISCON_BE 0x0 |

| #define nDISNYET_R 0x0 |

| #define nDMA0_INT 0x0 |

| #define nDMA1_INT 0x0 |

| #define nDMA2_INT 0x0 |

| #define nDMA3_INT 0x0 |

| #define nDMA4_INT 0x0 |

| #define nDMA5_INT 0x0 |

| #define nDMA6_INT 0x0 |

| #define nDMA7_INT 0x0 |

| #define nDMA_ENA 0x0 |

| #define nDMAREQ_ENA_R 0x0 |

| #define nDMAREQ_ENA_T 0x0 |

| #define nDMAREQMODE_R 0x0 |

| #define nDMAREQMODE_RH 0x0 |

| #define nDMAREQMODE_T 0x0 |

| #define nDRIVE_VBUS_OFF 0x0 |

| #define nDRIVE_VBUS_OFF_ENA 0x0 |

| #define nDRIVE_VBUS_ON 0x0 |

| #define nDRIVE_VBUS_ON_ENA 0x0 |

| #define nENABLE_SUSPENDM 0x0 |

| #define nEP0_TX 0x0 |

| #define nEP0_TX_E 0x0 |

| #define nEP1_RX 0x0 |

| #define nEP1_RX_E 0x0 |

| #define nEP1_RX_ENA 0x0 |

| #define nEP1_TX 0x0 |

| #define nEP1_TX_E 0x0 |

| #define nEP1_TX_ENA 0x0 |

| #define nEP2_RX 0x0 |

| #define nEP2_RX_E 0x0 |

| #define nEP2_RX_ENA 0x0 |

| #define nEP2_TX 0x0 |

| #define nEP2_TX_E 0x0 |

| #define nEP2_TX_ENA 0x0 |

| #define nEP3_RX 0x0 |

| #define nEP3_RX_E 0x0 |

| #define nEP3_RX_ENA 0x0 |

| #define nEP3_TX 0x0 |

| #define nEP3_TX_E 0x0 |

| #define nEP3_TX_ENA 0x0 |

| #define nEP4_RX 0x0 |

| #define nEP4_RX_E 0x0 |

| #define nEP4_RX_ENA 0x0 |

| #define nEP4_TX 0x0 |

| #define nEP4_TX_E 0x0 |

| #define nEP4_TX_ENA 0x0 |

| #define nEP5_RX 0x0 |

| #define nEP5_RX_E 0x0 |

| #define nEP5_RX_ENA 0x0 |

| #define nEP5_TX 0x0 |

| #define nEP5_TX_E 0x0 |

| #define nEP5_TX_ENA 0x0 |

| #define nEP6_RX 0x0 |

| #define nEP6_RX_E 0x0 |

| #define nEP6_RX_ENA 0x0 |

| #define nEP6_TX 0x0 |

| #define nEP6_TX_E 0x0 |

| #define nEP6_TX_ENA 0x0 |

| #define nEP7_RX 0x0 |

| #define nEP7_RX_E 0x0 |

| #define nEP7_RX_ENA 0x0 |

| #define nEP7_TX 0x0 |

| #define nEP7_TX_E 0x0 |

| #define nEP7_TX_ENA 0x0 |

| #define nERROR_H 0x0 |

| #define nERROR_RH 0x0 |

| #define nERROR_TH 0x0 |

| #define nFIFO_FULL_R 0x0 |

| #define nFIFO_NOT_EMPTY_T 0x0 |

| #define nFLUSHFIFO 0x0 |

| #define nFLUSHFIFO_R 0x0 |

| #define nFLUSHFIFO_T 0x0 |

| #define nFORCE_DATATOGGLE_T 0x0 |

| #define nFSDEV 0x0 |

| #define nGLOBAL_ENA 0x0 |

| #define nHOST_MODE 0x0 |

| #define nHOST_REQ 0x0 |

| #define nHS_ENABLE 0x0 |

| #define nHS_MODE 0x0 |

| #define nINCOMPRX_R 0x0 |

| #define nINCOMPRX_RH 0x0 |

| #define nINCOMPTX_T 0x0 |

| #define nINT_ENA 0x0 |

| #define nISO_R 0x0 |

| #define nISO_T 0x0 |

| #define nISO_UPDATE 0x0 |

| #define nLSDEV 0x0 |

| #define nMODE 0x0 |

| #define nNAK_TIMEOUT_H 0x0 |

| #define nNAK_TIMEOUT_TH 0x0 |

| #define nOVERRUN_R 0x0 |

| #define nREQPKT_H 0x0 |

| #define nREQPKT_RH 0x0 |

| #define nRESET 0x0 |

| #define nRESET_OR_BABLE_B 0x0 |

| #define nRESET_OR_BABLE_BE 0x0 |

| #define nRESUME_B 0x0 |

| #define nRESUME_BE 0x0 |

| #define nRESUME_MODE 0x0 |

| #define nRXPKTRDY 0x0 |

| #define nRXPKTRDY_R 0x0 |

| #define nSENDSTALL 0x0 |

| #define nSERVICED_RXPKTRDY 0x0 |

| #define nSERVICED_SETUPEND 0x0 |

| #define nSESSION 0x0 |

| #define nSESSION_REQ_B 0x0 |

| #define nSESSION_REQ_BE 0x0 |

| #define nSETUPEND 0x0 |

| #define nSETUPPKT_H 0x0 |

| #define nSOF_B 0x0 |

| #define nSOF_BE 0x0 |

| #define nSOFT_CONN 0x0 |

| #define nSTALL_RECEIVED_H 0x0 |

| #define nSTALL_RECEIVED_RH 0x0 |

| #define nSTALL_RECEIVED_TH 0x0 |

| #define nSTALL_SEND_R 0x0 |

| #define nSTALL_SEND_T 0x0 |

| #define nSTALL_SENT 0x0 |

| #define nSTALL_SENT_R 0x0 |

| #define nSTALL_SENT_T 0x0 |

| #define nSTATUSPKT_H 0x0 |

| #define nSUSPEND_B 0x0 |

| #define nSUSPEND_BE 0x0 |

| #define nSUSPEND_MODE 0x0 |

| #define nTXPKTRDY 0x0 |

| #define nTXPKTRDY_T 0x0 |

| #define nUNDERRUN_T 0x0 |

| #define nVBUS0 0x0 |

| #define nVBUS1 0x0 |

| #define nVBUS_ERROR_B 0x0 |

| #define nVBUS_ERROR_BE 0x0 |

| #define OctetsReceivedAll EMAC_RXC_ALLOCT |

| #define OctetsReceivedOK EMAC_RXC_OCTET |

| #define OctetsTransmittedAll EMAC_TXC_ALLOCT |

| #define OctetsTransmittedOK EMAC_TXC_OCTET |

| #define OutOfRangeLengthField EMAC_RXC_LNERRO |

| #define OVERRUN_R 0x4 |

| #define PAM 0x00000040 |

| #define PAUSEMACCtrlFramesReceived EMAC_RXC_PAUSE |

| #define PBF 0x00000400 |

| #define PCF 0x00000004 |

| #define PHYAD 0x0000F800 |

| #define PHYIE 0x00000001 |

| #define PHYINT 0x00000001 |

| #define PR 0x00000080 |

| #define PROTOCOL_R 0xc |

| #define PROTOCOL_T 0xc |

| #define PSF 0x00000800 |

| #define RAF 0x00001000 |

| #define RE 0x00000001 |

| #define REGAD 0x000007C0 |

| #define REQPKT_H 0x20 |

| #define REQPKT_RH 0x20 |

| #define RESET 0x8 |

| #define RESET_OR_BABLE_B 0x4 |

| #define RESET_OR_BABLE_BE 0x4 |

| #define RESUME_B 0x2 |

| #define RESUME_BE 0x2 |

| #define RESUME_MODE 0x4 |

| #define RMII 0x01000000 |

| #define RMII_10 0x02000000 |

| #define RSTC 0x00000001 |

| #define RWKE 0x00000004 |

| #define RWKS 0x00000F00 |

| #define RX_ACCEPT 0x80000000 |

| #define RX_ADDR 0x00080000 |

| #define RX_ALIGN 0x00008000 |

| #define RX_ALIGN_CNT 0x00000004 |

| #define RX_ALLF_CNT 0x00004000 |

| #define RX_ALLO_CNT 0x00008000 |

| #define RX_BROAD 0x02000000 |

| #define RX_BROAD_CNT 0x00000080 |

| #define RX_COMP 0x00001000 |

| #define RX_COUNT 0x1fff |

| #define RX_CRC 0x00010000 |

| #define RX_CTL 0x04000000 |

| #define RX_DMAO 0x00100000 |

| #define RX_EQ64_CNT 0x00040000 |

| #define RX_FCS_CNT 0x00000002 |

| #define RX_FRAG 0x00040000 |

| #define RX_FRLEN 0x000007FF |

| #define RX_GE1024_CNT 0x00800000 |

| #define RX_IRL_CNT 0x00000100 |

| #define RX_LATE 0x00400000 |

| #define RX_LEN 0x00020000 |

| #define RX_LONG 0x00004000 |

| #define RX_LONG_CNT 0x00000400 |

| #define RX_LOST_CNT 0x00000010 |

| #define RX_LT1024_CNT 0x00400000 |

| #define RX_LT128_CNT 0x00080000 |

| #define RX_LT256_CNT 0x00100000 |

| #define RX_LT512_CNT 0x00200000 |

| #define RX_MACCTL_CNT 0x00000800 |

| #define RX_MULTI 0x01000000 |

| #define RX_MULTI_CNT 0x00000040 |

| #define RX_OCTET_CNT 0x00000008 |

| #define RX_OK 0x00002000 |

| #define RX_OK_CNT 0x00000001 |

| #define RX_OPCODE_CTL 0x00001000 |

| #define RX_ORL_CNT 0x00000200 |

| #define RX_PAUSE_CNT 0x00002000 |

| #define RX_PHY 0x00200000 |

| #define RX_POLL_INTERVAL 0xff |

| #define RX_RANGE 0x00800000 |

| #define RX_SHORT_CNT 0x00020000 |

| #define RX_TYPE 0x10000000 |

| #define RX_TYPED_CNT 0x00010000 |

| #define RX_UCTL 0x08000000 |

| #define RX_UNI_CNT 0x00000020 |

| #define RX_VLAN1 0x20000000 |

| #define RX_VLAN2 0x40000000 |

| #define RXCKS 0x00000004 |

| #define RXDMAERR 0x00000020 |

| #define RXDWA 0x00000002 |

| #define RXFSINT 0x00000004 |

| #define RXPKTRDY 0x1 |

| #define RXPKTRDY_R 0x1 |

| #define SELECTED_ENDPOINT 0xf |

| #define SENDSTALL 0x20 |

| #define SERVICED_RXPKTRDY 0x40 |

| #define SERVICED_SETUPEND 0x80 |

| #define SESSION 0x1 |

| #define SESSION_REQ_B 0x40 |

| #define SESSION_REQ_BE 0x40 |

| #define SET_FLCPAUSE | ( | x | ) | (((x)&0xFFFF)<< 16) |

| #define SET_MDCDIV | ( | x | ) | (((x)&0x3F)<< 8) |

| #define SET_PHYAD | ( | x | ) | (((x)&0x1F)<< 11 ) |

| #define SET_REGAD | ( | x | ) | (((x)&0x1F)<< 6 ) |

| #define SET_WF0_CRC | ( | x | ) | (((x)&0xFFFF)<< 0 ) |

| #define SET_WF0_OFF | ( | x | ) | (((x)&0xFF)<< 0 ) |

| #define SET_WF1_CRC | ( | x | ) | (((x)&0xFFFF)<< 16 ) |

| #define SET_WF1_OFF | ( | x | ) | (((x)&0xFF)<< 8 ) |

| #define SET_WF2_CRC | ( | x | ) | (((x)&0xFFFF)<< 0 ) |

| #define SET_WF2_OFF | ( | x | ) | (((x)&0xFF)<< 16 ) |

| #define SET_WF3_CRC | ( | x | ) | (((x)&0xFFFF)<< 16 ) |

| #define SET_WF3_OFF | ( | x | ) | (((x)&0xFF)<< 24 ) |

| #define SET_WF_OFFS | ( | x0, | |||

| x1, | |||||

| x2, | |||||

| x3 | ) | (SET_WF0_OFF((x0))|SET_WF1_OFF((x1))|SET_WF2_OFF((x2))|SET_WF3_OFF((x3))) |

| #define SETUPEND 0x10 |

| #define SETUPPKT_H 0x8 |

| #define SingleCollisionFrames EMAC_TXC_1COL |

| #define SOF_B 0x8 |

| #define SOF_BE 0x8 |

| #define SOFT_CONN 0x40 |

| #define STABUSY 0x00000001 |

| #define STADATA 0x0000FFFF |

| #define STADISPRE 0x00000004 |

| #define STAIE 0x00000008 |

| #define STALL_RECEIVED_H 0x4 |

| #define STALL_RECEIVED_RH 0x40 |

| #define STALL_RECEIVED_TH 0x20 |

| #define STALL_SEND_R 0x20 |

| #define STALL_SEND_T 0x10 |

| #define STALL_SENT 0x4 |

| #define STALL_SENT_R 0x40 |

| #define STALL_SENT_T 0x20 |

| #define STAOP 0x00000002 |

| #define STATUSPKT_H 0x40 |

| #define STMDONE 0x00000080 |

| #define SUSPEND_B 0x1 |

| #define SUSPEND_BE 0x1 |

| #define SUSPEND_MODE 0x2 |

| #define TARGET_EP_NO_R 0xf |

| #define TARGET_EP_NO_T 0xf |

| #define TE 0x00010000 |

| #define TX_ABORT_CNT 0x00400000 |

| #define TX_ABORTC_CNT 0x00000040 |

| #define TX_ALLF_CNT 0x00004000 |

| #define TX_ALLO_CNT 0x00008000 |

| #define TX_BROAD 0x00000040 |

| #define TX_BROAD_CNT 0x00000800 |

| #define TX_CCNT 0x00000F00 |

| #define TX_COMP 0x00000001 |

| #define TX_COUNT 0x1fff |

| #define TX_CRS 0x00002000 |

| #define TX_CRS_CNT 0x00000100 |

| #define TX_DEFER 0x00001000 |

| #define TX_DEFER_CNT 0x00000010 |

| #define TX_DMAU 0x00000010 |

| #define TX_ECOLL 0x00000004 |

| #define TX_EDEFER 0x00000020 |

| #define TX_EQ64_CNT 0x00010000 |

| #define TX_EXDEF_CTL 0x00001000 |

| #define TX_FRLEN 0x07FF0000 |

| #define TX_GE1024_CNT 0x00200000 |

| #define TX_LATE 0x00000008 |

| #define TX_LATE_CNT 0x00000020 |

| #define TX_LOSS 0x00004000 |

| #define TX_LOST_CNT 0x00000080 |

| #define TX_LT1024_CNT 0x00100000 |

| #define TX_LT128_CNT 0x00020000 |

| #define TX_LT256_CNT 0x00040000 |

| #define TX_LT512_CNT 0x00080000 |

| #define TX_MACCTL_CNT 0x00002000 |

| #define TX_MACE 0x00000010 |

| #define TX_MCOLL_CNT 0x00000004 |

| #define TX_MULTI 0x00000080 |

| #define TX_MULTI_CNT 0x00000400 |

| #define TX_OCTET_CNT 0x00000008 |

| #define TX_OK 0x00000002 |

| #define TX_OK_CNT 0x00000001 |

| #define TX_POLL_INTERVAL 0xff |

| #define TX_RETRY 0x00008000 |

| #define TX_SCOLL_CNT 0x00000002 |

| #define TX_UNI_CNT 0x00000200 |

| #define TxAbortedFrames EMAC_TXC_ABORT |

| #define TXDMAERR 0x00000040 |

| #define TXFSINT 0x00000008 |

| #define TXPKTRDY 0x2 |

| #define TXPKTRDY_T 0x1 |

| #define TypedFramesReceived EMAC_RXC_TYPED |

| #define UNDERRUN_T 0x4 |

| #define UnicastFramesReceivedOK EMAC_RXC_UNICST |

| #define UnicastFramesXmittedOK EMAC_TXC_UNICST |

| #define UnsupportedOpcodesReceived EMAC_RXC_OPCODE |

| #define USB_APHY_CALIB 0xffc039e4 |

| #define USB_APHY_CNTRL 0xffc039e0 |

| #define USB_APHY_CNTRL2 0xffc039e8 |

| #define USB_COUNT0 0xffc03850 |

| #define USB_CSR0 0xffc03844 |

| #define USB_DMA0ADDRHIGH 0xffc03c0c |

| #define USB_DMA0ADDRLOW 0xffc03c08 |

| #define USB_DMA0CONTROL 0xffc03c04 |

| #define USB_DMA0COUNTHIGH 0xffc03c14 |

| #define USB_DMA0COUNTLOW 0xffc03c10 |

| #define USB_DMA1ADDRHIGH 0xffc03c2c |

| #define USB_DMA1ADDRLOW 0xffc03c28 |

| #define USB_DMA1CONTROL 0xffc03c24 |

| #define USB_DMA1COUNTHIGH 0xffc03c34 |

| #define USB_DMA1COUNTLOW 0xffc03c30 |

| #define USB_DMA2ADDRHIGH 0xffc03c4c |

| #define USB_DMA2ADDRLOW 0xffc03c48 |

| #define USB_DMA2CONTROL 0xffc03c44 |

| #define USB_DMA2COUNTHIGH 0xffc03c54 |

| #define USB_DMA2COUNTLOW 0xffc03c50 |

| #define USB_DMA3ADDRHIGH 0xffc03c6c |

| #define USB_DMA3ADDRLOW 0xffc03c68 |

| #define USB_DMA3CONTROL 0xffc03c64 |

| #define USB_DMA3COUNTHIGH 0xffc03c74 |

| #define USB_DMA3COUNTLOW 0xffc03c70 |

| #define USB_DMA4ADDRHIGH 0xffc03c8c |

| #define USB_DMA4ADDRLOW 0xffc03c88 |

| #define USB_DMA4CONTROL 0xffc03c84 |

| #define USB_DMA4COUNTHIGH 0xffc03c94 |

| #define USB_DMA4COUNTLOW 0xffc03c90 |

| #define USB_DMA5ADDRHIGH 0xffc03cac |

| #define USB_DMA5ADDRLOW 0xffc03ca8 |

| #define USB_DMA5CONTROL 0xffc03ca4 |

| #define USB_DMA5COUNTHIGH 0xffc03cb4 |

| #define USB_DMA5COUNTLOW 0xffc03cb0 |

| #define USB_DMA6ADDRHIGH 0xffc03ccc |

| #define USB_DMA6ADDRLOW 0xffc03cc8 |

| #define USB_DMA6CONTROL 0xffc03cc4 |

| #define USB_DMA6COUNTHIGH 0xffc03cd4 |

| #define USB_DMA6COUNTLOW 0xffc03cd0 |

| #define USB_DMA7ADDRHIGH 0xffc03cec |

| #define USB_DMA7ADDRLOW 0xffc03ce8 |

| #define USB_DMA7CONTROL 0xffc03ce4 |

| #define USB_DMA7COUNTHIGH 0xffc03cf4 |

| #define USB_DMA7COUNTLOW 0xffc03cf0 |

| #define USB_DMA_INTERRUPT 0xffc03c00 |

| #define USB_EP0_FIFO 0xffc03880 |

| #define USB_EP1_FIFO 0xffc03888 |

| #define USB_EP2_FIFO 0xffc03890 |

| #define USB_EP3_FIFO 0xffc03898 |

| #define USB_EP4_FIFO 0xffc038a0 |

| #define USB_EP5_FIFO 0xffc038a8 |

| #define USB_EP6_FIFO 0xffc038b0 |

| #define USB_EP7_FIFO 0xffc038b8 |

| #define USB_EP_NI0_RXCOUNT 0xffc03a10 |

| #define USB_EP_NI0_RXCSR 0xffc03a0c |

| #define USB_EP_NI0_RXINTERVAL 0xffc03a20 |

| #define USB_EP_NI0_RXMAXP 0xffc03a08 |

| #define USB_EP_NI0_RXTYPE 0xffc03a1c |

| #define USB_EP_NI0_TXCOUNT 0xffc03a28 |

| #define USB_EP_NI0_TXCSR 0xffc03a04 |

| #define USB_EP_NI0_TXINTERVAL 0xffc03a18 |

| #define USB_EP_NI0_TXMAXP 0xffc03a00 |

| #define USB_EP_NI0_TXTYPE 0xffc03a14 |

| #define USB_EP_NI1_RXCOUNT 0xffc03a50 |

| #define USB_EP_NI1_RXCSR 0xffc03a4c |

| #define USB_EP_NI1_RXINTERVAL 0xffc03a60 |

| #define USB_EP_NI1_RXMAXP 0xffc03a48 |

| #define USB_EP_NI1_RXTYPE 0xffc03a5c |

| #define USB_EP_NI1_TXCOUNT 0xffc03a68 |

| #define USB_EP_NI1_TXCSR 0xffc03a44 |

| #define USB_EP_NI1_TXINTERVAL 0xffc03a58 |

| #define USB_EP_NI1_TXMAXP 0xffc03a40 |

| #define USB_EP_NI1_TXTYPE 0xffc03a54 |

| #define USB_EP_NI2_RXCOUNT 0xffc03a90 |

| #define USB_EP_NI2_RXCSR 0xffc03a8c |

| #define USB_EP_NI2_RXINTERVAL 0xffc03aa0 |

| #define USB_EP_NI2_RXMAXP 0xffc03a88 |

| #define USB_EP_NI2_RXTYPE 0xffc03a9c |

| #define USB_EP_NI2_TXCOUNT 0xffc03aa8 |

| #define USB_EP_NI2_TXCSR 0xffc03a84 |

| #define USB_EP_NI2_TXINTERVAL 0xffc03a98 |

| #define USB_EP_NI2_TXMAXP 0xffc03a80 |

| #define USB_EP_NI2_TXTYPE 0xffc03a94 |

| #define USB_EP_NI3_RXCOUNT 0xffc03ad0 |

| #define USB_EP_NI3_RXCSR 0xffc03acc |

| #define USB_EP_NI3_RXINTERVAL 0xffc03ae0 |

| #define USB_EP_NI3_RXMAXP 0xffc03ac8 |

| #define USB_EP_NI3_RXTYPE 0xffc03adc |

| #define USB_EP_NI3_TXCOUNT 0xffc03ae8 |

| #define USB_EP_NI3_TXCSR 0xffc03ac4 |

| #define USB_EP_NI3_TXINTERVAL 0xffc03ad8 |

| #define USB_EP_NI3_TXMAXP 0xffc03ac0 |

| #define USB_EP_NI3_TXTYPE 0xffc03ad4 |

| #define USB_EP_NI4_RXCOUNT 0xffc03b10 |

| #define USB_EP_NI4_RXCSR 0xffc03b0c |

| #define USB_EP_NI4_RXINTERVAL 0xffc03b20 |

| #define USB_EP_NI4_RXMAXP 0xffc03b08 |

| #define USB_EP_NI4_RXTYPE 0xffc03b1c |

| #define USB_EP_NI4_TXCOUNT 0xffc03b28 |

| #define USB_EP_NI4_TXCSR 0xffc03b04 |

| #define USB_EP_NI4_TXINTERVAL 0xffc03b18 |

| #define USB_EP_NI4_TXMAXP 0xffc03b00 |

| #define USB_EP_NI4_TXTYPE 0xffc03b14 |

| #define USB_EP_NI5_RXCOUNT 0xffc03b50 |

| #define USB_EP_NI5_RXCSR 0xffc03b4c |

| #define USB_EP_NI5_RXINTERVAL 0xffc03b60 |

| #define USB_EP_NI5_RXMAXP 0xffc03b48 |

| #define USB_EP_NI5_RXTYPE 0xffc03b5c |

| #define USB_EP_NI5_TXCOUNT 0xffc03b68 |

| #define USB_EP_NI5_TXCSR 0xffc03b44 |

| #define USB_EP_NI5_TXINTERVAL 0xffc03b58 |

| #define USB_EP_NI5_TXMAXP 0xffc03b40 |

| #define USB_EP_NI5_TXTYPE 0xffc03b54 |

| #define USB_EP_NI6_RXCOUNT 0xffc03b90 |

| #define USB_EP_NI6_RXCSR 0xffc03b8c |

| #define USB_EP_NI6_RXINTERVAL 0xffc03ba0 |

| #define USB_EP_NI6_RXMAXP 0xffc03b88 |

| #define USB_EP_NI6_RXTYPE 0xffc03b9c |

| #define USB_EP_NI6_TXCOUNT 0xffc03ba8 |

| #define USB_EP_NI6_TXCSR 0xffc03b84 |

| #define USB_EP_NI6_TXINTERVAL 0xffc03b98 |

| #define USB_EP_NI6_TXMAXP 0xffc03b80 |

| #define USB_EP_NI6_TXTYPE 0xffc03b94 |

| #define USB_EP_NI7_RXCOUNT 0xffc03bd0 |

| #define USB_EP_NI7_RXCSR 0xffc03bcc |

| #define USB_EP_NI7_RXINTERVAL 0xffc03bf0 |

| #define USB_EP_NI7_RXMAXP 0xffc03bc8 |

| #define USB_EP_NI7_RXTYPE 0xffc03bdc |

| #define USB_EP_NI7_TXCOUNT 0xffc03bf8 |

| #define USB_EP_NI7_TXCSR 0xffc03bc4 |

| #define USB_EP_NI7_TXINTERVAL 0xffc03bd8 |

| #define USB_EP_NI7_TXMAXP 0xffc03bc0 |

| #define USB_EP_NI7_TXTYPE 0xffc03bd4 |

| #define USB_FADDR 0xffc03800 |

| #define USB_FRAME 0xffc03820 |

| #define USB_FS_EOF1 0xffc03954 |

| #define USB_GLOBAL_CTL 0xffc03830 |

| #define USB_GLOBINTR 0xffc0382c |

| #define USB_HS_EOF1 0xffc03950 |

| #define USB_INDEX 0xffc03824 |

| #define USB_INTRRX 0xffc0380c |

| #define USB_INTRRXE 0xffc03814 |

| #define USB_INTRTX 0xffc03808 |

| #define USB_INTRTXE 0xffc03810 |

| #define USB_INTRUSB 0xffc03818 |

| #define USB_INTRUSBE 0xffc0381c |

| #define USB_LINKINFO 0xffc03948 |

| #define USB_LS_EOF1 0xffc03958 |

| #define USB_NAKLIMIT0 0xffc03858 |

| #define USB_OTG_DEV_CTL 0xffc03900 |

| #define USB_OTG_VBUS_IRQ 0xffc03904 |

| #define USB_OTG_VBUS_MASK 0xffc03908 |

| #define USB_PHY_TEST 0xffc039ec |

| #define USB_PLLOSC_CTRL 0xffc039f0 |

| #define USB_POWER 0xffc03804 |

| #define USB_RX_MAX_PACKET 0xffc03848 |

| #define USB_RXCOUNT 0xffc03850 |

| #define USB_RXCSR 0xffc0384c |

| #define USB_RXINTERVAL 0xffc03860 |

| #define USB_RXTYPE 0xffc0385c |

| #define USB_SRP_CLKDIV 0xffc039f4 |

| #define USB_TESTMODE 0xffc03828 |

| #define USB_TX_MAX_PACKET 0xffc03840 |

| #define USB_TXCOUNT 0xffc03868 |

| #define USB_TXCSR 0xffc03844 |

| #define USB_TXINTERVAL 0xffc03858 |

| #define USB_TXTYPE 0xffc03854 |

| #define USB_VPLEN 0xffc0394c |

| #define VBUS0 0x8 |

| #define VBUS1 0x10 |

| #define VBUS_ERROR_B 0x80 |

| #define VBUS_ERROR_BE 0x80 |

| #define WAKEDET 0x00000010 |

| #define WF0_CRC 0x0000FFFF |

| #define WF0_E 0x00000001 |

| #define WF0_OFF 0x000000FF |

| #define WF0_T 0x00000008 |

| #define WF1_CRC 0xFFFF0000 |

| #define WF1_E 0x00000100 |

| #define WF1_OFF 0x0000FF00 |

| #define WF1_T 0x00000800 |

| #define WF2_CRC 0x0000FFFF |

| #define WF2_E 0x00010000 |

| #define WF2_OFF 0x00FF0000 |

| #define WF2_T 0x00080000 |

| #define WF3_CRC 0xFFFF0000 |

| #define WF3_E 0x01000000 |

| #define WF3_OFF 0xFF000000 |

| #define WF3_T 0x08000000 |

1.4.7

1.4.7